### **General Description**

The MAX19507 dual-channel, analog-to-digital converter (ADC) provides 8-bit resolution and a maximum sample rate of 130Msps.

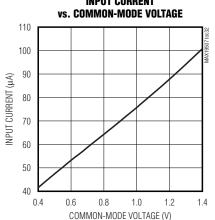

The MAX19507 analog input accepts a wide 0.4V to 1.4V input common-mode voltage range, allowing DCcoupled inputs for a wide range of RF, IF, and baseband front-end components. The MAX19507 provides excellent dynamic performance from baseband to high input frequencies beyond 400MHz, making the device ideal for zero-intermediate frequency (ZIF) and highintermediate frequency (IF) sampling applications. The typical signal-to-noise ratio (SNR) performance is 49.8dBFS and typical spurious-free dynamic range (SFDR) is 69dBc at  $f_{IN} = 70MHz$  and  $f_{CLK} = 130MHz$ .

The MAX19507 operates from a 1.8V supply. Additionally, an integrated, self-sensing voltage regulator allows operation from a 2.5V to 3.3V supply (AVDD). The digital output drivers operate on an independent supply voltage (OVDD) over the 1.8V to 3.5V range. The analog power consumption is only 74mW per channel at  $V_{AVDD} = 1.8V$ . In addition to low operating power, the MAX19507 consumes only 1mW in powerdown mode and 21mW in standby mode.

Various adjustments and feature selections are available through programmable registers that are accessed through the 3-wire serial-port interface. Alternatively, the serial-port interface can be disabled, with the three inputs available to select output mode, data format, and clock-divider mode. Data outputs are available through a dual parallel CMOS-compatible output data bus that can also be configured as a single multiplexed parallel CMOS bus.

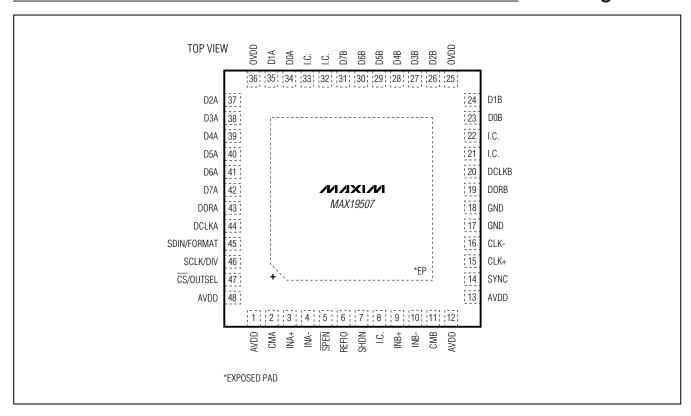

The MAX19507 is available in a small 7mm x 7mm, 48pin thin QFN package and is specified over the -40°C to +85°C extended temperature range.

Refer to the MAX19515, MAX19516, and MAX19517 data sheets for pin- and feature-compatible 10-bit, 65Msps, 100Msps, and 130Msps versions, respectively. Refer to the MAX19505 and MAX19506 data sheets for pin- and feature-compatible 8-bit, 65Msps and 100Msps versions, respectively.

### **Applications**

IF and Baseband Communications, Including Cellular Base Stations and Point-to-Point Microwave Receivers

Ultrasound and Medical Imaging

Portable Instrumentation and Low-Power Data Acquisition

Digital Set-Top Boxes

#### **Features**

- ♦ Very-Low-Power Operation (74mW/Channel at 130Msps)

- ♦ 1.8V or 2.5V to 3.3V Analog Supply

- **♦ Excellent Dynamic Performance** 49.8dBFS SNR at 70MHz 69dBc SFDR at 70MHz

- ♦ User-Programmable Adjustments and Feature Selection through an SPI™ Interface

- ♦ Selectable Data Bus (Dual CMOS or Single **Multiplexed CMOS)**

- **♦ DCLK Output and Programmable Data Output Timing Simplifies High-Speed Digital Interface**

- **♦ Very Wide Input Common-Mode Voltage Range** (0.4V to 1.4V)

- ♦ Very High Analog Input Bandwidth (> 850MHz)

- ♦ Single-Ended or Differential Analog Inputs

- **♦** Single-Ended or Differential Clock Input

- ♦ Divide-by-One (DIV1), Divide-by-Two (DIV2), and Divide-by-Four (DIV4) Clock Modes

- **♦ Two's Complement, Gray Code, and Offset Binary Output Data Format**

- ♦ Out-of-Range Indicator (DOR)

- **♦ CMOS Output Internal Termination Options** (Programmable)

- **♦** Reversible Bit Order (Programmable)

- ◆ Data Output Test Patterns

- ♦ Small 7mm x 7mm, 48-Pin Thin QFN Package with **Exposed Pad**

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX19507ETM+ | -40°C to +85°C | 48 TQFN-EP* |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

Pin Configuration appears at end of data sheet.

SPI is a trademark of Motorola, Inc.

MIXIM

<sup>\*</sup>EP = Exposed pad.

### **ABSOLUTE MAXIMUM RATINGS**

| OVDD, AVDD to GND0.3V to +3.6V                            |

|-----------------------------------------------------------|

| CMA, CMB, REFIO, INA+, INA-, INB+,                        |

| INB- to GND0.3V to +2.1V                                  |

| CLK+, CLK-, SYNC, SPEN, CS, SCLK, SDIN                    |

| to GND0.3V to the lower of (VAVDD + 0.3V) and +3.6V       |

| DCLKA, DCLKB, D7A-D0A, D7B-D0B, DORA, DORB                |

| to GND0.3V to the lower of ( $V_{OVDD}$ + 0.3V) and +3.6V |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)<br>48-Pin Thin QFN, 7mm x 7mm x 0.8mm (c | derate 40mW/°C |

|------------------------------------------------------------------------------------------------|----------------|

| above +70°C)                                                                                   | 3200mW         |

| Operating Temperature Range                                                                    | 40°C to +85°C  |

| Junction Temperature                                                                           | +150°C         |

| Storage Temperature Range                                                                      |                |

| Lead Temperature (soldering, 10s)                                                              |                |

| Soldering Temperature (reflow)                                                                 | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{AVDD} = V_{OVDD} = 1.8V, internal reference, differential clock, V_{CLK} = 1.5V_{P-P}, f_{CLK} = 130MHz, A_{IN} = -0.5dBFS, data output termination = 50<math>\Omega$ ,  $T_{A} = -40^{\circ}$ C to +85°C, unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}$ C.) (Note 1)

| PARAMETER                          | SYMBOL            | CONDITIONS                                                     | MIN   | TYP  | MAX  | UNITS            |  |

|------------------------------------|-------------------|----------------------------------------------------------------|-------|------|------|------------------|--|

| DC ACCURACY                        | . N               |                                                                |       |      |      |                  |  |

| Resolution                         |                   |                                                                |       | 8    |      | Bits             |  |

| Integral Nonlinearity              | INL               | f <sub>IN</sub> = 3MHz                                         | -0.3  | ±0.1 | +0.3 | LSB              |  |

| Differential Nonlinearity          | DNL               | f <sub>IN</sub> = 3MHz                                         | -0.3  | ±0.1 | +0.3 | LSB              |  |

| Offset Error                       | OE                | Internal reference -0.4 ±0.1 +0.4                              |       | +0.4 | %FS  |                  |  |

| Gain Error                         | GE                | External reference = 1.25V                                     | -1.5  | ±0.3 | +1.5 | %FS              |  |

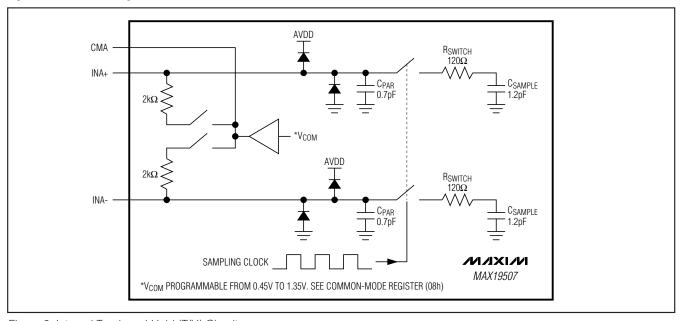

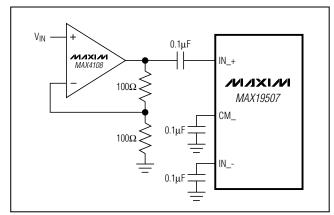

| ANALOG INPUTS (INA+, INA-, IN      | B+, INB-) (Fi     | gure 3)                                                        |       |      |      |                  |  |

| Differential Input-Voltage Range   | V <sub>DIFF</sub> | Differential or single-ended inputs                            |       | 1.5  |      | V <sub>P-P</sub> |  |

| Common-Mode Input-Voltage<br>Range | Vсм               | (Note 2) 0.4                                                   |       |      | 1.4  | V                |  |

| James to Decistors of              | D                 | Fixed resistance, common mode, and differential mode           | > 100 |      | kΩ   |                  |  |

| Input Resistance                   | R <sub>IN</sub>   | Differential input resistance, common mode connected to inputs | 4     |      |      | NS2              |  |

| Input Current                      | I <sub>IN</sub>   | Switched capacitance common-mode input current, each input     | 74    |      |      | μА               |  |

| Input Canaditana                   | CPAR              | Fixed capacitance to ground, each input                        | 0.7   |      |      | ,,,[             |  |

| Input Capacitance                  | CSAMPLE           | Switched capacitance, each input                               | 1.2   |      |      | pF               |  |

| CONVERSION RATE                    |                   |                                                                |       |      |      |                  |  |

| Maximum Clock Frequency            | fCLK              | 130                                                            |       |      | MHz  |                  |  |

| Minimum Clock Frequency            | fCLK              |                                                                | 65    |      | MHz  |                  |  |

| Data Latency                       |                   | Figures 9, 10                                                  |       | 9    | •    | Cycles           |  |

2 \_\_\_\_\_\_M/XI/M

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{OVDD} = 1.8V, internal reference, differential clock, V_{CLK} = 1.5V_{P-P}, f_{CLK} = 130MHz, A_{IN} = -0.5dBFS, data output termination = <math>50\Omega$ ,  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 1)

| PARAMETER                                                 | SYMBOL CONDITIONS |                                                             | MIN  | TYP   | MAX   | UNITS  |  |

|-----------------------------------------------------------|-------------------|-------------------------------------------------------------|------|-------|-------|--------|--|

| DYNAMIC PERFORMANCE                                       | •                 |                                                             | •    |       |       | •      |  |

| Small-Signal Noise Floor                                  | SSNF              | f <sub>IN</sub> = 70MHz, < -35dBFS                          |      | -49.8 |       | dBFS   |  |

|                                                           |                   | f <sub>IN</sub> = 3MHz                                      |      | 49.8  |       |        |  |

| Signal-to-Noise Ratio                                     | SNR               | f <sub>IN</sub> = 70MHz                                     | 49.0 | 49.8  |       | dBFS   |  |

|                                                           |                   | $f_{IN} = 175MHz$                                           |      | 49.8  |       |        |  |

| O                                                         |                   | f <sub>IN</sub> = 3MHz                                      |      | 49.3  |       |        |  |

| Signal-to-Noise Plus Distortion Ratio                     | SINAD             | f <sub>IN</sub> = 70MHz                                     | 48.5 | 49.3  |       | dB     |  |

| Hallo                                                     |                   | $f_{IN} = 175MHz$                                           |      | 49.3  |       |        |  |

|                                                           |                   | $f_{IN} = 3MHz$                                             |      | 77.0  |       |        |  |

| Spurious-Free Dynamic Range (2nd and 3rd Harmonic)        | SFDR1             | f <sub>IN</sub> = 70MHz                                     | 65.0 | 77.0  |       | dBc    |  |

| (Zhu ahu shu Haimbhio)                                    |                   | $f_{IN} = 175MHz$                                           |      | 77.0  |       |        |  |

| Spurious-Free Dynamic Range<br>(4th and Higher Harmonics) |                   | f <sub>IN</sub> = 3MHz                                      |      | 69.0  |       |        |  |

|                                                           | SFDR2             | f <sub>IN</sub> = 70MHz                                     | 64.0 | 69.0  |       | dBc    |  |

|                                                           |                   | $f_{IN} = 175MHz$                                           |      | 69.0  |       |        |  |

|                                                           | HD2               | f <sub>IN</sub> = 3MHz                                      |      | -78.0 |       |        |  |

| Second Harmonic                                           |                   | f <sub>IN</sub> = 70MHz                                     |      | -78.0 | -65.0 | dBc    |  |

|                                                           |                   | $f_{IN} = 175MHz$                                           |      | -78.0 |       |        |  |

|                                                           |                   | $f_{IN} = 3MHz$                                             |      | -82.0 |       |        |  |

| Third Harmonic                                            | HD3               | f <sub>IN</sub> = 70MHz                                     |      | -82.0 | -65.0 | dBc    |  |

|                                                           |                   | $f_{IN} = 175MHz$                                           |      | -80.0 |       |        |  |

|                                                           |                   | f <sub>IN</sub> = 3MHz                                      |      | -72.0 |       |        |  |

| Total Harmonic Distortion                                 | THD               | $f_{IN} = 70MHz$                                            |      | -72.0 | -63.0 | dBc    |  |

|                                                           |                   | $f_{IN} = 175MHz$                                           |      | -72.0 |       |        |  |

| Third Code a late was a division                          | IMO               | $f_{IN} = 70MHz \pm 1.5MHz, -7dBFS$                         |      | -80   |       | -ID -  |  |

| Third-Order Intermodulation                               | IM3               | $f_{IN} = 175MHz \pm 2.5MHz, -7dBFS$                        |      | -75   |       | dBc    |  |

| Full-Power Bandwidth                                      | FPBW              | R <sub>SOURCE</sub> = $50\Omega$ differential, -3dB rolloff |      | 850   |       | MHz    |  |

| Aperture Delay                                            | t <sub>AD</sub>   |                                                             |      | 850   |       | ps     |  |

| Aperture Jitter                                           | taj               |                                                             |      | 0.3   |       | psRMS  |  |

| Overdrive Recovery Time                                   |                   | ±10% beyond full scale                                      |      | 1     |       | Cycles |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{OVDD} = 1.8V, internal reference, differential clock, V_{CLK} = 1.5V_{P-P}, f_{CLK} = 130MHz, A_{IN} = -0.5dBFS, data output termination = <math>50\Omega$ ,  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 1)

| PARAMETER                                                       | SYMBOL              | CONDITIONS                                               | MIN  | TYP                   | MAX  | UNITS            |

|-----------------------------------------------------------------|---------------------|----------------------------------------------------------|------|-----------------------|------|------------------|

| INTERCHANNEL CHARACTERIS                                        | TICS                |                                                          |      |                       |      |                  |

| Crosstalle                                                      |                     | f <sub>INA</sub> or f <sub>INB</sub> = 70MHz at -1dBFS   |      | 95                    |      | dD.a             |

| Crosstalk                                                       |                     | f <sub>INA</sub> or f <sub>INB</sub> = 175MHz at -1dBFS  |      | 85                    |      | - dBc            |

| Gain Match                                                      |                     | f <sub>IN</sub> = 70MHz                                  |      | ±0.05                 |      | dB               |

| Offset Match                                                    |                     | f <sub>IN</sub> = 70MHz                                  |      | ±0.2                  |      | %FSR             |

| Phase Match                                                     |                     | f <sub>IN</sub> = 70MHz                                  |      | ±0.5                  |      | Degrees          |

| ANALOG OUTPUTS (CMA, CMB)                                       | 1                   |                                                          |      |                       |      |                  |

| CMA, CMB Output Voltage                                         | V <sub>COM</sub>    | Default programmable setting                             | 0.85 | 0.9                   | 0.95 | V                |

| INTERNAL REFERENCE                                              |                     |                                                          |      |                       |      |                  |

| REFIO Output Voltage                                            | V <sub>REFOUT</sub> |                                                          | 1.23 | 1.25                  | 1.27 | V                |

| REFIO Temperature Coefficient                                   | TCREF               |                                                          |      | < ±60                 |      | ppm/°C           |

| EXTERNAL REFERENCE                                              |                     |                                                          |      |                       |      |                  |

| REFIO Input-Voltage Range                                       | VREFIN              |                                                          |      | 1.25 +5/<br>-10%      |      | V                |

| REFIO Input Resistance                                          | R <sub>REFIN</sub>  |                                                          |      | 10<br>±20%            |      | kΩ               |

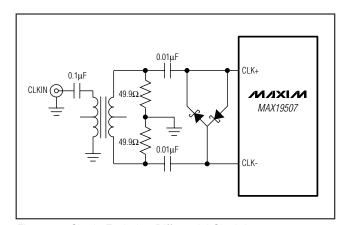

| CLOCK INPUTS (CLK+, CLK-)—[                                     | DIFFERENTIA         | AL MODE                                                  | l .  |                       |      | 1                |

| Differential Clock Input Voltage                                |                     |                                                          |      | 0.4 to 2.0            |      | V <sub>P-P</sub> |

| Differential Input Common-Mode                                  |                     | Self-biased                                              |      | 1.2                   |      | .,,              |

| Voltage                                                         |                     | DC-coupled clock signal                                  |      | 1.0 to 1.4            |      | V                |

|                                                                 |                     | Differential, default                                    |      | 10                    |      | kΩ               |

| Input Resistance                                                | RCLK                | Differential, programmable internal termination selected |      | 100                   |      | Ω                |

|                                                                 |                     | Common mode                                              |      | 9                     |      | kΩ               |

| Input Capacitance                                               | CCLK                | To ground, each input                                    |      | 3                     |      | pF               |

| CLOCK INPUTS (CLK+, CLK-)—5                                     | SINGLE-END          | ED MODE (V <sub>CLK</sub> - < 0.1V)                      | •    |                       |      |                  |

| Single-Ended Mode Selection<br>Threshold (V <sub>CLK</sub> -)   |                     |                                                          |      |                       | 0.1  | V                |

| Allowable Logic Swing (V <sub>CLK+</sub> )                      |                     |                                                          |      | 0 - V <sub>AVDD</sub> |      | V                |

| Single-Ended Clock Input High<br>Threshold (V <sub>CLK+</sub> ) |                     |                                                          | 1.5  |                       |      | V                |

| Single-Ended Clock Input Low<br>Threshold (V <sub>CLK+</sub> )  |                     |                                                          |      |                       | 0.3  | V                |

|                                                                 |                     | $V_{CLK+} = V_{AVDD} = 1.8V \text{ or } 3.3V$            |      |                       | +0.5 |                  |

| Input Leakage (CLK+)                                            |                     | $V_{CLK+} = 0V$                                          | -0.5 |                       |      | μA               |

| Input Leakage (CLK-)                                            |                     | V <sub>CLK</sub> -= 0V                                   | -150 |                       | -50  | μΑ               |

| Input Capacitance (CLK+)                                        |                     |                                                          |      | 3                     |      | pF               |

4 \_\_\_\_\_\_*NIXI/*N

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{OVDD} = 1.8V, internal reference, differential clock, V_{CLK} = 1.5V_{P-P}, f_{CLK} = 130MHz, A_{IN} = -0.5dBFS, data output termination = <math>50\Omega$ ,  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 1)

| PARAMETER                                         | SYMBOL                      | CONDITIONS                                                                               | MIN                     | TYP                    | MAX  | UNITS |  |

|---------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------|-------------------------|------------------------|------|-------|--|

| CLOCK INPUT (SYNC)                                | •                           |                                                                                          | •                       |                        |      | •     |  |

| Allowable Logic Swing                             |                             |                                                                                          |                         | 0 - V <sub>AVD</sub>   | )    | V     |  |

| Sync Clock Input High Threshold                   |                             |                                                                                          | 1.5                     |                        |      | V     |  |

| Sync Clock Input Low Threshold                    |                             |                                                                                          |                         |                        | 0.3  | V     |  |

| Input Lockago                                     |                             | V <sub>SYNC</sub> = V <sub>AVDD</sub> = 1.8V or 3.3V                                     |                         |                        | +0.5 |       |  |

| Input Leakage                                     |                             | V <sub>SYNC</sub> = 0V                                                                   | -0.5                    |                        |      | μΑ    |  |

| Input Capacitance                                 |                             |                                                                                          |                         | 4.5                    |      | рF    |  |

| $\textbf{DIGITAL INPUTS (SHDN, \overline{SPEN})}$ |                             |                                                                                          |                         |                        |      |       |  |

| Allowable Logic Swing                             |                             |                                                                                          |                         | 0 - V <sub>AVD</sub> [ | )    | V     |  |

| Input High Threshold                              |                             |                                                                                          | 1.5                     |                        |      | V     |  |

| Input Low Threshold                               |                             |                                                                                          |                         |                        | 0.3  | V     |  |

| Input Leakage                                     |                             | V <sub>SHDN</sub> /V <del>SPEN</del> = V <sub>AVDD</sub> = 1.8V or 3.3V                  |                         |                        | +0.5 |       |  |

| Input Leakage                                     |                             | V <sub>SHDN</sub> /V <del>SPEN</del> = 0V                                                | -0.5                    |                        |      | μΑ    |  |

| Input Capacitance                                 | CDIN                        |                                                                                          |                         | 3                      |      | рF    |  |

| SERIAL-PORT INPUTS (SCLK, S                       | DIN, CS, whe                | ere SPEN = 0V)—SERIAL-PORT CONTROL N                                                     | <b>IODE</b>             |                        |      |       |  |

| Allowable Logic Swing                             |                             |                                                                                          |                         | 0 - V <sub>AVD</sub>   | )    | V     |  |

| Input High Threshold                              |                             |                                                                                          | 1.5                     |                        |      | V     |  |

| Input Low Threshold                               |                             |                                                                                          |                         |                        | 0.3  | V     |  |

| Innest Lockons                                    |                             | V <sub>SCLK</sub> /V <sub>SDIN</sub> /V <sub>CS</sub> = V <sub>AVDD</sub> = 1.8V or 3.3V |                         |                        | +0.5 |       |  |

| Input Leakage                                     |                             | V <sub>SCLK</sub> /V <sub>SDIN</sub> /V <del>CS</del> = 0V                               | -0.5                    |                        |      | μΑ    |  |

| Input Capacitance                                 | C <sub>DIN</sub>            |                                                                                          |                         | 3                      |      | рF    |  |

| SERIAL-PORT INPUTS (SCLK, S                       | DIN, CS, whe                | ere SPEN = V <sub>AVDD</sub> )—PARALLEL CONTROL                                          | MODE (Fig               | gure 5)                |      |       |  |

| Inner the Drelle in Commont                       |                             | V <sub>SCLK</sub> /V <sub>SDIN</sub> /V <del>CS</del> = V <sub>AVDD</sub> = 1.8V         | 7                       | 12                     | 17   |       |  |

| Input Pullup Current                              |                             | V <sub>SCLK</sub> /V <sub>SDIN</sub> /V <del>CS</del> = V <sub>AVDD</sub> = 3.3V         | 16                      | 21                     | 26   | μΑ    |  |

|                                                   |                             | V <sub>SCLK</sub> /V <sub>SDIN</sub> /V <sub>CS</sub> = 0V, V <sub>AVDD</sub> = 1.8V     | -65                     | -50                    | -35  |       |  |

| Input Pulldown Current                            |                             | V <sub>SCLK</sub> /V <sub>SDIN</sub> /V <del>CS</del> = 0V, V <sub>AVDD</sub> = 3.3V     | -105                    | -90                    | -75  | μΑ    |  |

|                                                   | 1 .,                        | $V_{AVDD} = 1.8V$                                                                        | 1.35                    | 1.45                   | 1.55 |       |  |

| Open-Circuit Voltage                              | Voc                         | V <sub>A</sub> V <sub>DD</sub> = 3.3V                                                    | 2.58                    | 2.68                   | 2.78 | V     |  |

| DIGITAL OUTPUTS (CMOS MOD                         | E 75Ω, D0–D                 | 7 (A and B Channel), DCLKA, DCLKB, DOR.                                                  | A, DORB)                |                        |      |       |  |

| Output-Voltage Low                                | V <sub>OL</sub>             | I <sub>SINK</sub> = 200µA                                                                |                         |                        | 0.2  | V     |  |

| Output-Voltage High                               | V <sub>OH</sub>             | ISOURCE = 200µA                                                                          | V <sub>OVDD</sub> - 0.2 |                        |      | V     |  |

| TI 01 1 1 0 :                                     |                             | V <sub>OVDD</sub> applied                                                                |                         |                        | +0.5 |       |  |

| Three-State Leakage Current                       | e Current I <sub>LEAK</sub> | GND applied                                                                              | -0.5                    |                        |      | μΑ    |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{OVDD} = 1.8V, internal reference, differential clock, V_{CLK} = 1.5V_{P-P}, f_{CLK} = 130MHz, A_{IN} = -0.5dBFS, data output termination = <math>50\Omega$ ,  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 1)

| PARAMETER                               | SYMBOL          | CONDITIONS                                               | MIN       | TYP       | MAX  | UNITS  |

|-----------------------------------------|-----------------|----------------------------------------------------------|-----------|-----------|------|--------|

| POWER-MANAGEMENT CHARA                  | CTERISTICS      |                                                          |           |           |      |        |

| Wake-Up Time from Shutdown              | twake           | Internal reference, C <sub>REFIO</sub> = 0.1μF (10τ)     |           | 5         |      | ms     |

| Wake-Up Time from Standby               | twake           | Internal reference                                       |           | 15        |      | μs     |

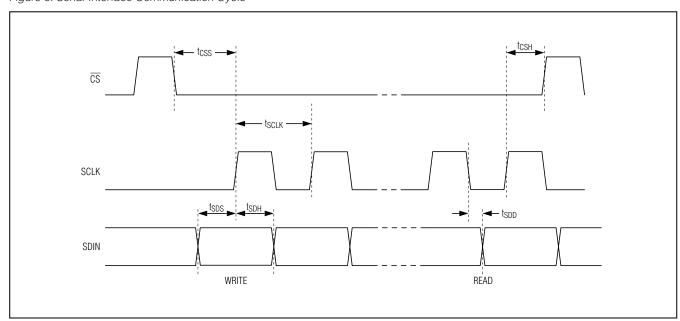

| SERIAL-PORT INTERFACE TIMIN             | NG (Note 2) (   | Figure 7)                                                |           |           |      |        |

| SCLK Period                             | tsclk           |                                                          | 50        |           |      | ns     |

| SCLK to CS Setup Time                   | tcss            |                                                          | 10        |           |      | ns     |

| SCLK to CS Hold Time                    | tCSH            |                                                          | 10        |           |      | ns     |

| SDIN to SCLK Setup Time                 | tsds            | Serial-data write                                        | 10        |           |      | ns     |

| SDIN to SCLK Hold Time                  | tsdh            | Serial-data write                                        | 0         |           |      | ns     |

| SCLK to SDIN Output Data Delay          | tsdd            | Serial-data read                                         |           |           | 10   | ns     |

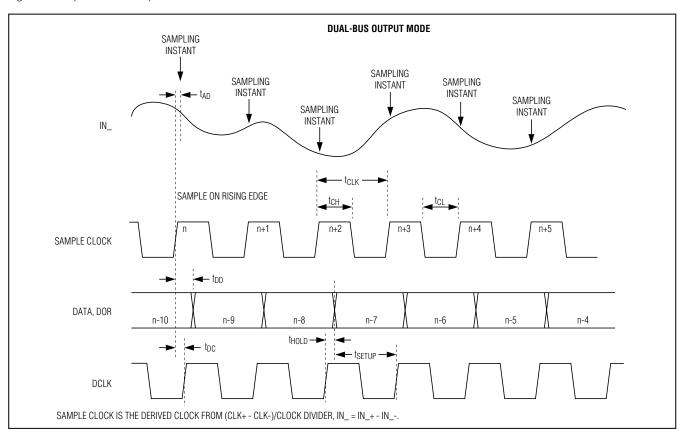

| TIMING CHARACTERISTICS—DU               | JAL BUS PA      | RALLEL MODE (Figure 9), (Default Timing s                | see Table | 5)        |      |        |

| Clock Pulse-Width High                  | tCH             |                                                          |           | 3.85      |      | ns     |

| Clock Pulse-Width Low                   | tcL             |                                                          |           | 3.85      |      | ns     |

| Clock Duty Cycle                        | tCH/tCLK        |                                                          |           | 30 to 70  |      | %      |

| Data Delay After Rising Edge of         | +               | C <sub>L</sub> = 10pF, V <sub>OVDD</sub> = 1.8V (Note 2) | 10.3      | 12.6      | 14.9 | 20     |

| CLK+                                    | t <sub>DD</sub> | $C_L = 10pF, V_{OVDD} = 3.3V$                            | 11.4      |           |      | ns     |

| Data to DCLK Setup Time                 | tSETUP          | C <sub>L</sub> = 10pF, V <sub>OVDD</sub> = 1.8V (Note 2) | 6.0       | 6.7       |      | ns     |

| Data to DCLK Hold Time                  | tHOLD           | C <sub>L</sub> = 10pF, V <sub>OVDD</sub> = 1.8V (Note 2) | 0.4       | 1.0       |      | ns     |

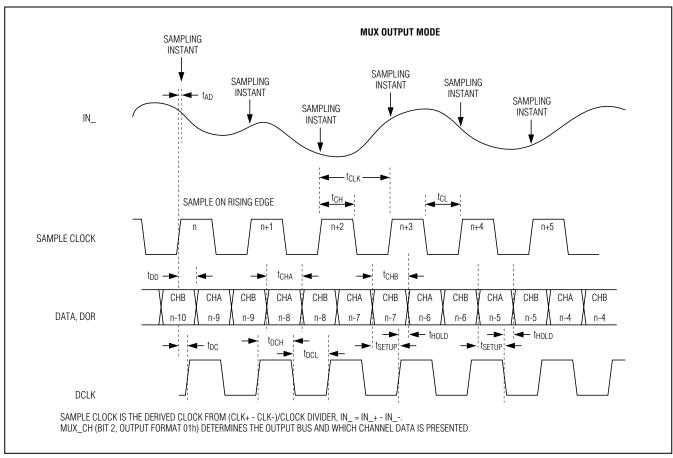

| TIMING CHARACTERISTICS—MI               | JLTIPLEXED      | BUS PARALLEL MODE (Figure 10), (Defau                    | It Timing | see Table | 5)   |        |

| Clock Pulse-Width High                  | tCH             |                                                          |           | 3.85      |      | ns     |

| Clock Pulse-Width Low                   | tcL             |                                                          |           | 3.85      |      | ns     |

| Clock Duty Cycle                        | tcH/tcLK        |                                                          |           | 30 to 70  |      | %      |

| Data Delay After Rising Edge of         |                 | C <sub>L</sub> = 10pF, V <sub>OVDD</sub> = 1.8V (Note 2) | 6.9       | 9.2       | 11.5 |        |

| CLK+                                    | tDD             | C <sub>L</sub> = 10pF, V <sub>OVDD</sub> = 3.3V          |           | 8.5       |      | ns     |

| Data to DCLK Setup Time                 | tSETUP          | C <sub>L</sub> = 10pF, V <sub>OVDD</sub> = 1.8V (Note 2) | 1.3       | 2.3       |      | ns     |

| Data to DCLK Hold Time                  | thold           | C <sub>L</sub> = 10pF, V <sub>OVDD</sub> = 1.8V (Note 2) | 0.7       | 1.5       |      | ns     |

| DCLK Duty Cycle                         | tDCH/tCLK       | C <sub>L</sub> = 10pF, V <sub>OVDD</sub> = 1.8V (Note 2) | 38        | 50        | 64   | %      |

| MUX Data Duty Cycle                     | tCHA/tCLK       | C <sub>L</sub> = 10pF, V <sub>OVDD</sub> = 1.8V (Note 2) | 38        | 50        | 62   | %      |

| TIMING CHARACTERISTICS—SY               | NCHRONIZA       | ATION (Figure 12)                                        | •         |           |      |        |

| Setup Time for Valid Clock Edge         | tsuv            | Edge mode (Note 2)                                       | 0.7       |           |      | ns     |

| Hold-Off Time for Invalid Clock<br>Edge | tHO             | Edge mode (Note 2)                                       | 0.5       |           |      | ns     |

| Minimum Synchronization Pulse Width     |                 | Relative to input clock period                           |           | 2         |      | Cycles |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{OVDD} = 1.8V, internal reference, differential clock, V_{CLK} = 1.5V_{P-P}, f_{CLK} = 130MHz, A_{IN} = -0.5dBFS, data output termination = <math>50\Omega$ ,  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 1)

| PARAMETER                     | SYMBOL            | CONDITIONS                                                           | MIN | TYP     | MAX | UNITS |  |

|-------------------------------|-------------------|----------------------------------------------------------------------|-----|---------|-----|-------|--|

| POWER REQUIREMENTS            |                   |                                                                      |     |         |     |       |  |

|                               |                   | Low-level VAVDD                                                      | 1.7 | 1.7 1.9 |     |       |  |

| Analog Supply Voltage         | Vavdd             | High-level V <sub>AVDD</sub> (regulator mode, invoked automatically) | 2.3 |         | 3.5 | V     |  |

| Digital Output Supply Voltage | Vovdd             |                                                                      | 1.7 |         | 3.5 | V     |  |

|                               |                   | Dual channel                                                         |     | 82      | 95  |       |  |

|                               |                   | Single channel active                                                |     | 48      |     | mA    |  |

| Analog Supply Current         | I <sub>AVDD</sub> | Standby mode                                                         |     | 11.5    | 15  |       |  |

|                               |                   | Power-down mode                                                      |     | 0.65    | 0.9 |       |  |

|                               |                   | Power-down mode, V <sub>AVDD</sub> = 3.3V                            |     | 1.6     |     |       |  |

|                               |                   | Dual channel                                                         |     | 148     | 171 |       |  |

|                               |                   | Dual channel, V <sub>AVDD</sub> = 3.3V                               |     | 271     |     |       |  |

| Analog Dower Dissipation      | Do.               | Single channel active                                                |     | 86      |     | mW    |  |

| Analog Power Dissipation      | PDA               | Standby mode                                                         |     | 21      | 27  | ITIVV |  |

|                               |                   | Power-down mode                                                      |     | 1.2     | 1.6 |       |  |

|                               |                   | Power-down mode, V <sub>AVDD</sub> = 3.3V                            |     | 2.9     |     |       |  |

| Digital Output Cupply Current | loves             | Dual-channel mode, C <sub>L</sub> = 10pF                             |     | 22      |     | m ^   |  |

| Digital Output Supply Current | lovdd             | Power-down mode                                                      |     | < 0.1   |     | mA    |  |

Note 1: Specifications T<sub>A</sub> ≥ +25°C guaranteed by production test, specifications T<sub>A</sub> < +25°C guaranteed by design and characterization.

Note 2: Guaranteed by design and characterization.

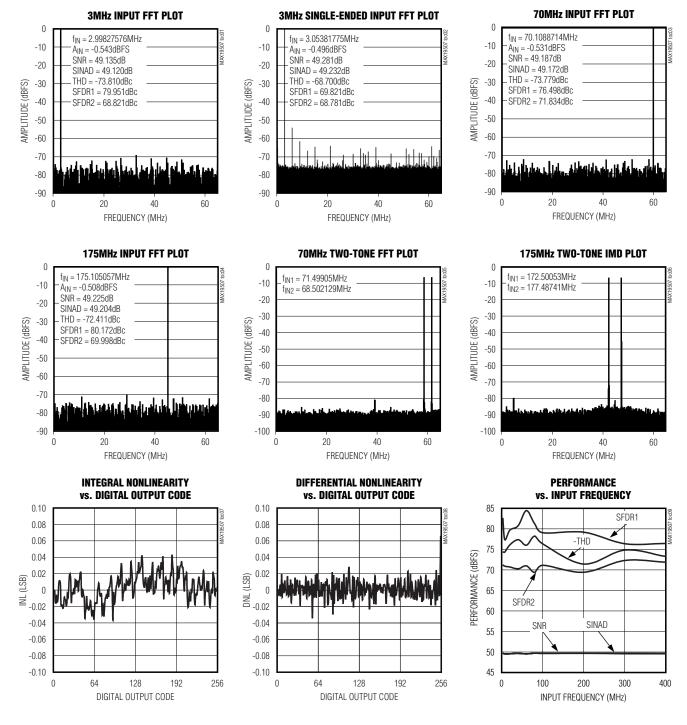

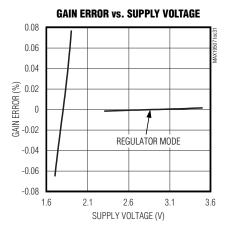

### **Typical Operating Characteristics**

(VAVDD = VOVDD = 1.8V), internal reference, differential clock, VCLK = 1.5VP-P, fCLK = 130MHz, AIN = -0.5dBFS, data output termination =  $50\Omega$ ,  $T_A = +25$ °C, unless otherwise noted.)

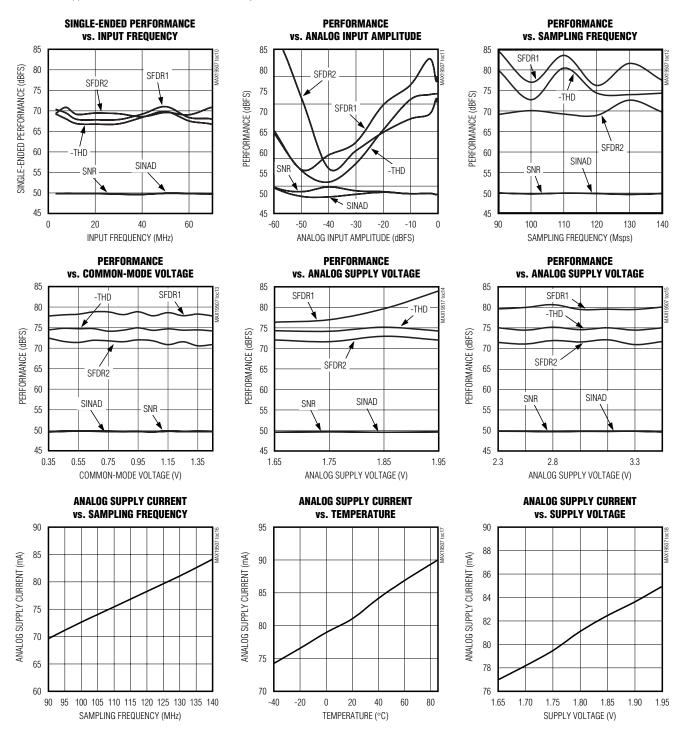

### **Typical Operating Characteristics (continued)**

$(V_{AVDD} = V_{OVDD} = 1.8V)$ , internal reference, differential clock,  $V_{CLK} = 1.5V_{P-P}$ ,  $f_{CLK} = 130MHz$ ,  $A_{IN} = -0.5dBFS$ , data output termination =  $50\Omega$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

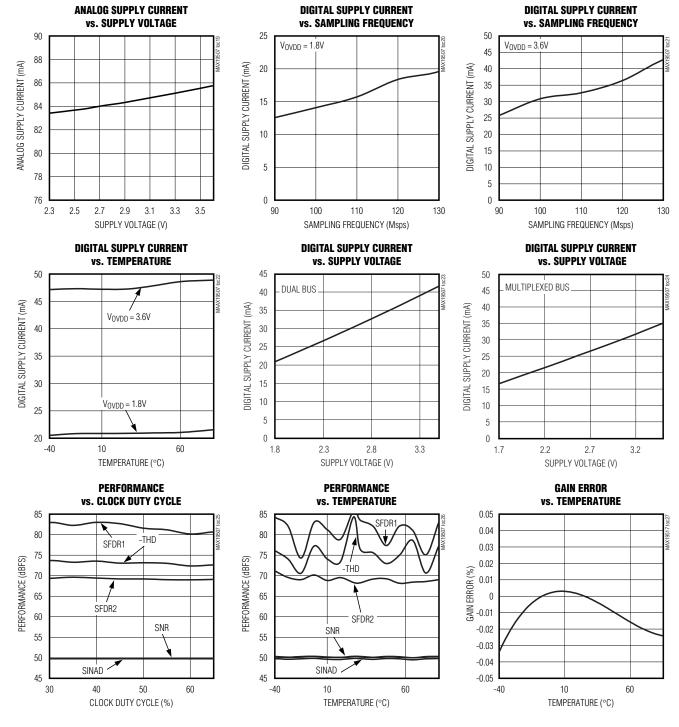

## Typical Operating Characteristics (continued)

$(V_{AVDD} = V_{OVDD} = 1.8V)$ , internal reference, differential clock,  $V_{CLK} = 1.5V_{P-P}$ ,  $f_{CLK} = 130MHz$ ,  $A_{IN} = -0.5dBFS$ , data output termination =  $50\Omega$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

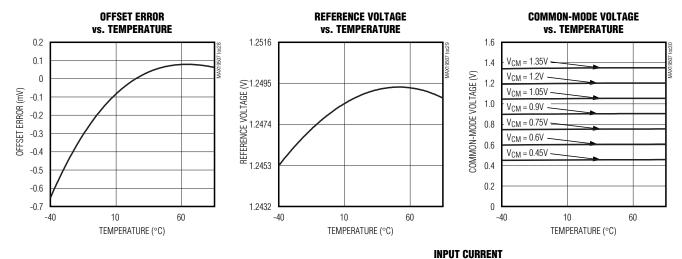

## Typical Operating Characteristics (continued)

$(V_{AVDD} = V_{OVDD} = 1.8V)$ , internal reference, differential clock,  $V_{CLK} = 1.5V_{P-P}$ ,  $f_{CLK} = 130MHz$ ,  $A_{IN} = -0.5dBFS$ , data output termination =  $50\Omega$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

## **Pin Description**

| PIN 1, 12, 13, 48 2 3 4 5 | AVDD CMA INA+ INA- SPEN | FUNCTION  Analog Supply Voltage. Bypass each AVDD input pair (1, 48) and (12, 13) to GND with 0.1µF.  Channel A Common-Mode Input-Voltage Reference  Channel A Positive Analog Input  Channel A Negative Analog Input |

|---------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 3 4                     | CMA<br>INA+<br>INA-     | Channel A Common-Mode Input-Voltage Reference Channel A Positive Analog Input                                                                                                                                         |

| 3 4                       | INA+                    | Channel A Positive Analog Input                                                                                                                                                                                       |

| 4                         | INA-                    |                                                                                                                                                                                                                       |

|                           |                         | Channel A Negative Analog Input                                                                                                                                                                                       |

| 5                         | SPEN                    |                                                                                                                                                                                                                       |

|                           |                         | Active-Low SPI Enable. Drive high to enable parallel programming mode.                                                                                                                                                |

| 6                         | REFIO                   | Reference Input/Output. To use internal reference, bypass to GND with a > 0.1µF capacitor. See the <i>Reference Input/Output (REFIO)</i> section for external reference adjustment.                                   |

| 7                         | SHDN                    | Active-High Power-Down. If SPEN is high (parallel programming mode), a register reset is initiated on the falling edge of SHDN.                                                                                       |

| 8                         | I.C.                    | Internally Connected. Leave unconnected.                                                                                                                                                                              |

| 9                         | INB+                    | Channel B Positive Analog Input                                                                                                                                                                                       |

| 10                        | INB-                    | Channel B Negative Analog Input                                                                                                                                                                                       |

| 11                        | CMB                     | Channel B Common-Mode Input-Voltage Reference                                                                                                                                                                         |

| 14                        | SYNC                    | Clock-Divider Mode Synchronization Input                                                                                                                                                                              |

| 15                        | CLK+                    | Clock Positive Input                                                                                                                                                                                                  |

| 16                        | CLK-                    | Clock Negative Input. If CLK- is connected to ground, CLK+ is a single-ended logic-level clock input. Otherwise, CLK+/CLK- are self-biased differential clock inputs.                                                 |

| 17, 18                    | GND                     | Ground. Connect all ground inputs and EP (exposed pad) together.                                                                                                                                                      |

| 19                        | DORB                    | Channel B Data Over Range                                                                                                                                                                                             |

| 20                        | DCLKB                   | Channel B Data Clock                                                                                                                                                                                                  |

| 21, 22                    | I.C.                    | Internally Connected. Leave unconnected.                                                                                                                                                                              |

| 23                        | D0B                     | Channel B Three-State Digital Output, Bit 0 (LSB)                                                                                                                                                                     |

| 24                        | D1B                     | Channel B Three-State Digital Output, Bit 1                                                                                                                                                                           |

| 25, 36                    | OVDD                    | Digital Supply Voltage. Bypass each OVDD input to GND with a 0.1µF capacitor.                                                                                                                                         |

| 26                        | D2B                     | Channel B Three-State Digital Output, Bit 2                                                                                                                                                                           |

| 27                        | D3B                     | Channel B Three-State Digital Output, Bit 3                                                                                                                                                                           |

| 28                        | D4B                     | Channel B Three-State Digital Output, Bit 4                                                                                                                                                                           |

| 29                        | D5B                     | Channel B Three-State Digital Output, Bit 5                                                                                                                                                                           |

| 30                        | D6B                     | Channel B Three-State Digital Output, Bit 6                                                                                                                                                                           |

| 31                        | D7B                     | Channel B Three-State Digital Output, Bit 7 (MSB)                                                                                                                                                                     |

| 32, 33                    | I.C.                    | Internally Connected. Leave unconnected.                                                                                                                                                                              |

| 34                        | D0A                     | Channel A Three-State Digital Output, Bit 0 (LSB)                                                                                                                                                                     |

| 35                        | D1A                     | Channel A Three-State Digital Output, Bit 1                                                                                                                                                                           |

| 37                        | D2A                     | Channel A Three-State Digital Output, Bit 2                                                                                                                                                                           |

| 38                        | D3A                     | Channel A Three-State Digital Output, Bit 3                                                                                                                                                                           |

| 39                        | D4A                     | Channel A Three-State Digital Output, Bit 4                                                                                                                                                                           |

### Pin Description (continued)

| PIN | NAME        | FUNCTION                                                                                                                                              |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40  | D5A         | Channel A Three-State Digital Output, Bit 5                                                                                                           |

| 41  | D6A         | Channel A Three-State Digital Output, Bit 6                                                                                                           |

| 42  | D7A         | Channel A Three-State Digital Output, Bit 7 (MSB)                                                                                                     |

| 43  | DORA        | Channel A Data Over Range                                                                                                                             |

| 44  | DCLKA       | Channel A Data Clock                                                                                                                                  |

| 45  | SDIN/FORMAT | SPI Data Input/Format. Serial-data input when SPEN is low. Output data format when SPEN is high.                                                      |

| 46  | SCLK/DIV    | Serial Clock/Clock Divider. Serial clock when SPEN is low. Clock divider when SPEN is high.                                                           |

| 47  | CS/OUTSEL   | Serial-Port Select/Data Output Mode. Serial-port select when \$\overline{SPEN}\$ is low. Data output mode selection when \$\overline{SPEN}\$ is high. |

| _   | EP          | Exposed Pad. Internally connected to GND. Connect to a large ground plane to maximize thermal performance.                                            |

### **Detailed Description**

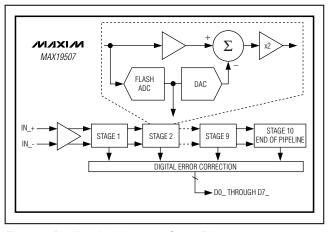

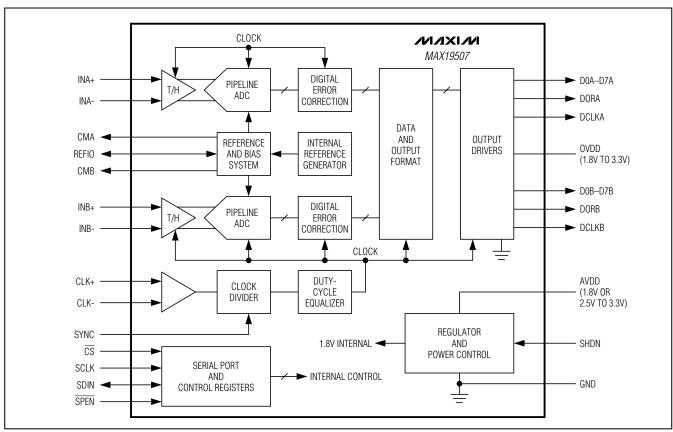

The MAX19507 uses a 10-stage, fully differential, pipelined architecture (Figure 1) that allows for high-speed conversion while minimizing power consumption. Samples taken at the inputs move progressively through the pipeline stages every half clock cycle. From input to output the total latency is 9 clock cycles. Each pipeline converter stage converts its input voltage to a digital output code. At every stage, except the last, the error between the input voltage and the digital output code is multiplied and passed on to the next pipeline stage. Digital error correction compensates for ADC comparator offsets in each pipeline stage and ensures no missing codes. Figure 2 shows the MAX19507 functional diagram.

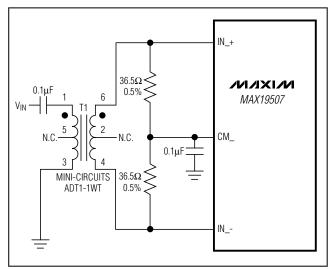

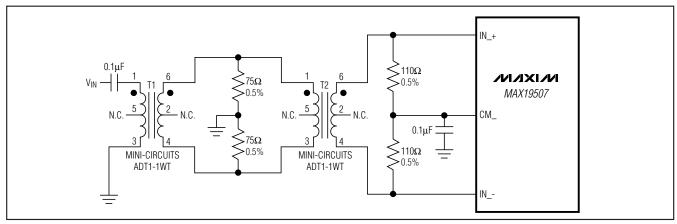

### Analog Inputs and Common-Mode Reference

Apply the analog input signal to the analog inputs (INA+/INA- or INB+/INB-), which are connected to the input sampling switch (Figure 3). When the input sampling switch is closed, the input signal is applied to the sampling capacitors through the input switch resistance. The input signal is sampled at the instant the input switch opens. The pipeline ADC processes the sampled voltage and the digital output result is available 9 clock cycles later. Before the input switch is closed to begin the next sampling cycle, the sampling capacitors are reset to the input common-mode potential.

Common-mode bias can be provided externally or internally through  $2k\Omega$  resistors. In DC-coupled applications, the signal source provides the external bias and the bias current. In AC-coupled applications, the input

Figure 1. Pipeline Architecture—Stage Blocks

current is supplied by the common-mode input voltage. For example, the input current can be supplied through the center tap of a transformer secondary winding. Alternatively, program the appropriate internal register through the serial-port interface to supply the input DC current through internal  $2k\Omega$  resistors (Figure 3). When the input current is supplied through the internal resistors, the input common-mode potential is reduced by the voltage drop across the resistors. The common-mode input reference voltage can be adjusted through programmable register settings from 0.45V to 1.35V in 0.15V increments. The default setting is 0.90V. Use this feature to provide a common-mode output reference to a DC-coupled driving circuit.

Figure 2. Functional Diagram

Figure 3. Internal Track-and-Hold (T/H) Circuit

14 \_\_\_\_\_\_\_ **/\!/**\!/\!

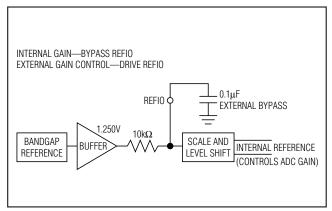

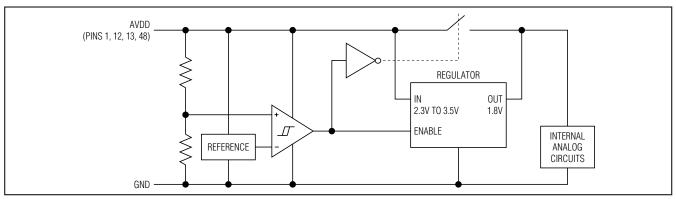

Figure 4. Simplified Reference Schematic

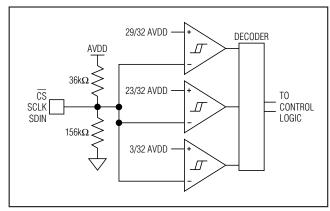

Figure 5. Simplified Parallel-Interface Input Schematic

### Table 1. Parallel-Interface Pin Functionality

| SPEN | SDIN/FORMAT | SCLK/DIV    | CS/OUTSEL   | DESCRIPTION                                                                                                                  |

|------|-------------|-------------|-------------|------------------------------------------------------------------------------------------------------------------------------|

| 0    | SDIN        | SCLK        | CS          | SPI interface active. Features are programmed through the serial port (see the <i>Serial Programming Interface</i> section). |

| 1    | 0           | Χ           | X           | Two's complement                                                                                                             |

| 1    | AVDD        | Χ           | X           | Offset binary                                                                                                                |

| 1    | Unconnected | X           | X           | Gray code                                                                                                                    |

| 1    | X           | 0           | X           | Clock divide-by-1                                                                                                            |

| 1    | X           | AVDD        | X           | Clock divide-by-2                                                                                                            |

| 1    | X           | Unconnected | X           | Clock divide-by-4                                                                                                            |

| 1    | X           | X           | 0           | CMOS (dual bus)                                                                                                              |

| 1    | X           | X           | AVDD        | MUX CMOS (channel A data bus)                                                                                                |

| 1    | Х           | Х           | Unconnected | MUX CMOS (channel B data bus)                                                                                                |

X = Don't care.

### Reference Input/Output (REFIO)

REFIO adjusts the reference potential, which, in turn, adjusts the full-scale range of the ADC. Figure 4 shows a simplified schematic of the reference system. An internal bandgap voltage generator provides an internal reference voltage. The bandgap potential is buffered and applied to REFIO through a  $10 \mathrm{k}\Omega$  resistor. Bypass REFIO with a  $0.1 \mu F$  capacitor to GND. The bandgap voltage is applied to a scaling and level-shift circuit, which creates internal reference potentials that establish the full-scale range of the ADC. Apply an external voltage on REFIO to trim the ADC full scale. The allowable adjustment range is +5/-15%. The REFIO-to-ADC gain transfer function is:

$V_{FS} = 1.5 \times [V_{REFIO}/1.25] \text{ Volts}$

### **Programming and Interface**

There are two ways to control the MAX19507 operating modes. Full feature selection is available using the SPI interface, while the parallel interface offers a limited set of commonly used features. The programming mode is selected using the SPEN input. Drive SPEN low for SPI interface; drive SPEN high for parallel interface.

#### Parallel Interface

The parallel interface offers a pin-programmable interface with a limited feature set. Connect SPEN to AVDD to enable the parallel interface. See Table 1 for pin functionality; see Figure 5 for a simplified parallel-interface input schematic.

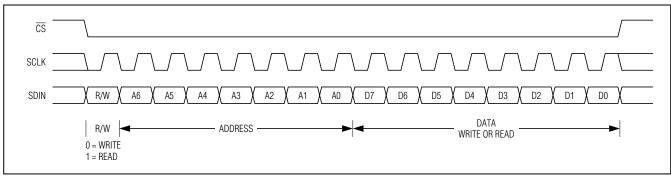

Figure 6. Serial-Interface Communication Cycle

Figure 7. Serial-Interface Timing Diagram

#### **Serial Programming Interface**

A serial interface programs the MAX19507 control registers through the  $\overline{\text{CS}}$ , SDIN, and SCLK inputs. Serial data is shifted into SDIN on the rising edge of SCLK when  $\overline{\text{CS}}$  is low. The MAX19507 ignores the data presented at SDIN and SCLK when  $\overline{\text{CS}}$  is high.  $\overline{\text{CS}}$  must transition high after each read/write operation. SDIN also serves as the serial-data output for reading control registers. The serial interface supports two-byte transfer in a communication cycle. The first byte is a control byte, containing the address and read/write instruction, written to the MAX19507. The second byte is a data byte and can be written to or read from the MAX19507.

Figure 6 shows a serial-interface communication cycle. The first SDIN bit clocked in establishes the communi-

cation cycle as either a write or read transaction (0 for write operation and 1 for read operation). The following 7 bits specify the address of the register to be written or read. The final 8 SDIN bits are the register data. All address and data bits are clocked in or out MSB first. During a read operation, the MAX19507 serial port drives read data (D7) into SDIN after the falling edge of SCLK following the 8th rising edge of SCLK. Since the minimum hold time on SDIN input is zero, the master can stop driving SDIN any time after the 8th rising edge of SCLK. Subsequent data bits are driven into SDIN on the falling edge of SCLK. Output data in a read operation is latched on the rising edge of SCLK. Figure 7 shows the detailed serial-interface timing diagram.

Register address 0Ah is a special-function register. Writing data 5Ah to register 0Ah initiates a register reset. When this operation is executed, all control regis-

ters are reset to default values. A read operation of register 0Ah returns a status byte with information described in Table 2.

Table 2. Register 0Ah Status Byte

| BIT NO. | VALUE  | DESCRIPTION                                                        |

|---------|--------|--------------------------------------------------------------------|

| 7       | 0      | Reserved                                                           |

| 6       | 0      | Reserved                                                           |

| 5       | 0 or 1 | 1 = ROM read in progress                                           |

| 4       | 0 or 1 | 1 = ROM read completed and register data is valid (checksum is OK) |

| 3       | 0      | Reserved                                                           |

| 2       | 1      | Reserved                                                           |

| 1       | 0 or 1 | Reserved                                                           |

| 0       | 0 or 1 | 1 = Duty-cycle equalizer DLL is locked                             |

### **User-Programmable Registers**

### **Table 3. User-Programmable Registers**

|         | 3           | 3                                     |

|---------|-------------|---------------------------------------|

| ADDRESS | POR DEFAULT | FUNCTION                              |

| 00h     | 00000011    | Power management                      |

| 01h     | 00000000    | Output format                         |

| 02h     | 00000000    | Digital output power management       |

| 03h     | 01101101    | Data/DCLK timing                      |

| 04h     | 00000000    | CHA data output termination control   |

| 05h     | 00000000    | CHB data output termination control   |

| 06h     | 00000000    | Clock divide/data format/test pattern |

| 07h     | Reserved    | Reserved—do not use                   |

| 08h     | 00000000    | Common mode                           |

| 0Ah     | _           | Software reset                        |

### **Power Management (00h)**

| BIT 7     | BIT 6      | BIT 5        | BIT 4        | BIT 3     | BIT 2      | BIT 1        | BIT 0        |

|-----------|------------|--------------|--------------|-----------|------------|--------------|--------------|

| HPS_SHDN1 | STBY_SHDN1 | CHB_ON_SHDN1 | CHA_ON_SHDN1 | HPS_SHDN0 | STBY_SHDN0 | CHB_ON_SHDN0 | CHA_ON_SHDN0 |

The SHDN input (pin 7) toggles between any two power-management states. The Power Management register defines each power-management state. In the

default state, SHDN = 1 shuts down the MAX19507 and SHDN = 0 returns to full power.

In addition to power management, the HPS\_SHDN1 and HPS\_SHDN0 activate an A+B adder mode. In this mode, the results from both channels are averaged.

The MUX\_CH bit selects which bus the (A+B)/2 data is presented.

#### **Control Bits:**

| HPS_SHDN0 | STBY_SHDN0 | CHA_ON_SHDN0                   | CHB_ON_SHDN0                           | SHDN INPUT = 0*                             |

|-----------|------------|--------------------------------|----------------------------------------|---------------------------------------------|

| HPS_SHDN1 | STBY_SHDN1 | CHA_ON_SHDN1                   | CHA_ON_SHDN1 CHB_ON_SHDN1 SHDN INPUT = |                                             |

| X         | 0          | 0                              | 0                                      | Complete power-down                         |

| 0         | 0          | 0                              | 1                                      | Channel B active, channel A full power-down |

| 0         | 0          | 1                              | 0                                      | Channel A active, channel B full power-down |

| 0         | X          | 1                              | 1                                      | Channels A and B active                     |

| 0         | 1          | 0 0 Channels A and B in standb |                                        | Channels A and B in standby mode            |

| 0         | 1          | 0                              | 1                                      | Channel B active, channel A standby         |

| 0         | 1          | 1                              | 0                                      | Channel A active, channel B standby         |

| 1         | 1          | 0                              | 0                                      | Channels A and B in standby mode            |

| 1         | X          | 1                              | X                                      | Channels A and B active, output is averaged |

| 1         | X          | X                              | 1                                      | Channels A and B active, output is averaged |

<sup>\*</sup>HPS\_SHDN0, STBY\_SHDN0, CHA\_ON\_SHDN0, and CHB\_ON\_SHDN0 are active when SHDN = 0.

**Note:** When HPS\_SHDN\_ = 1 (A+B adder mode), CHA\_ON\_SHDN\_ and CHB\_ON\_SHDN\_ must **BOTH** equal 0 for power-down or standby.

### Output Format (01h)

| BIT 7 | BIT 6 | BIT 5 | BIT 4       | BIT 3       | BIT 2  | BIT 1 | BIT 0 |

|-------|-------|-------|-------------|-------------|--------|-------|-------|

| 0     | 0     | 0     | BIT_ORDER_B | BIT_ORDER_A | MUX_CH | MUX   | 0     |

### Bit 7, 6, 5 Set to 0 for proper operation

Bit 4 BIT ORDER B: Reverse CHB output bit order

0 = Defined data bus pin order (default)

1 = Reverse data bus pin order

Bit 3 BIT\_ORDER\_A: Reverse CHA output bit order

0 = Defined data bus pin order (default)

1 = Reverse data bus pin order

Bit 2 MUX\_CH: Multiplexed data bus selection

0 = Multiplexed data output on CHA (CHA data presented first, followed by CHB data) (default)

1 = Multiplexed data output on CHB (CHB data presented first, followed by CHA data)

Bit 1 MUX: Digital output mode

0 = Dual data bus output mode (default)

1 = Single multiplexed data bus output mode

MUX CH selects the output bus

Bit 0 Set to 0 for proper operation

<sup>\*\*</sup>HPS\_SHDN1, STBY\_SHDN1, CHA\_ON\_SHDN1, and CHB\_ON\_SHDN1 are active when SHDN = 1.

X = Don't care.

## **Digital Output Power Management (02h)**

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3     | BIT 2     | BIT 1   | BIT 0    |

|-------|-------|-------|-------|-----------|-----------|---------|----------|

| Х     | X     | X     | Χ     | PD_DOUT_1 | PD_DOUT_0 | DIS_DOR | DIS_DCLK |

Bit 7-4 Don't care

Bit 3, 2 PD\_DOUT\_1, PD\_DOUT\_0: Power-down digital output state control

00 = Digital output three state (default)

01 = Digital output low

10 = Digital output three state

11 = Digital output high

Bit 1 DIS\_DOR: DOR driver disable

0 = DOR active (default)

1 = DOR disabled (three state)

Bit 0 DIS\_DCLK: DCLK driver disable

0 = DCLK active (default)

1 = DCLK disabled (three state)

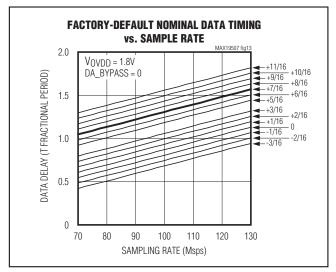

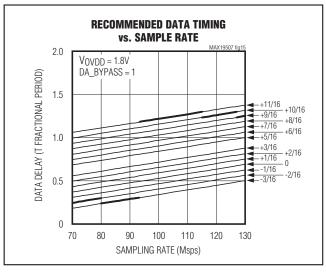

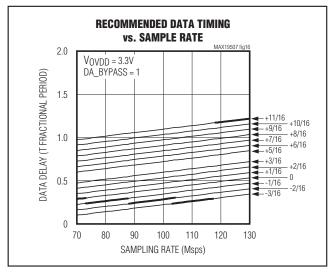

### Data/DCLK Timing (03h)

| BIT 7     | BIT 6      | BIT 5      | BIT 4      | BIT 3      | BIT 2   | BIT 1   | BIT 0   |

|-----------|------------|------------|------------|------------|---------|---------|---------|

| DA_BYPASS | DLY_HALF_T | DCLKTIME_2 | DCLKTIME_1 | DCLKTIME_0 | DTIME_2 | DTIME_1 | DTIME_0 |

Bit 7 DA\_BYPASS: Data aligner bypass

0 = Nominal (default)

1 = Bypasses data aligner delay line to minimize output data latency with respect to the input clock. Rising clock to data transition is approximately 6ns with DTIME = 000b settings

Bit 6 DLY\_HALF\_T: Data and DCLK delayed by T/2

0 = Normal, no delay

1 = Delays data and DCLK outputs by T/2 (default)

Disabled in MUX data bus mode

Bit 5, 4, 3 DCLKTIME\_2, DCLKTIME\_1, DCLKTIME\_0: DCLK timing adjust (controls both channels)

000 = Nominal

001 = +T/16

010 = +2T/16

011 = +3T/16

100 = Reserved, do not use

101 = -1T/16 (default)

110 = -2T/16

111 = -3T/16

Bit 2, 1, 0 DTIME\_2, DTIME\_1, DTIME\_0: Data timing adjust (controls both channels)

000 = Nominal

001 = +T/16

010 = +2T/16

011 = +3T/16

100 = Reserved, do not use

101 = -1T/16 (default)

110 = -2T/16

111 = -3T/16

## **CHA Data Output Termination Control (04h)**

| BIT 7 | BIT 6 | BIT 5       | BIT 4       | BIT 3       | BIT 2       | BIT 1       | BIT 0       |

|-------|-------|-------------|-------------|-------------|-------------|-------------|-------------|

| Х     | Χ     | CT_DCLK_2_A | CT_DCLK_1_A | CT_DCLK_0_A | CT_DATA_2_A | CT_DATA_1_A | CT_DATA_0_A |

Bit 7, 6 Don't care

Bit 5, 4, 3 CT\_DCLK\_2\_A, CT\_DCLK\_1\_A, CT\_DCLK\_0\_A: CHA DCLK termination control

$000 = 50\Omega$  (default)

$001 = 75\Omega$

$010 = 100\Omega$

$011 = 150\Omega$

$1xx = 300\Omega$

Bit 2, 1, 0 CT\_DATA\_2\_A, CT\_DATA\_1\_A, CT\_DATA\_0\_A: CHA data output termination control

$000 = 50\Omega$  (default)

$001 = 75\Omega$

$010 = 100\Omega$

$011 = 150\Omega$

$1xx = 300\Omega$

### **CHB Data Output Termination Control (05h)**

| BIT 7 | BIT 6 | BIT 5       | BIT 4       | BIT 3       | BIT 2       | BIT 1       | BIT 0       |

|-------|-------|-------------|-------------|-------------|-------------|-------------|-------------|

| X     | Х     | CT_DCLK_2_B | CT_DCLK_1_B | CT_DCLK_0_B | CT_DATA_2_B | CT_DATA_1_B | CT_DATA_0_B |

Bit 7, 6 Don't care

Bit 5, 4, 3 CT\_DCLK\_2\_B, CT\_DCLK\_1\_B, CT\_DCLK\_0\_B: CHB DCLK termination control

$000 = 50\Omega$  (default)

$001 = 75\Omega$

$010 = 100\Omega$

$011 = 150\Omega$

$1xx = 300\Omega$

Bit 2, 1, 0 CT\_DATA\_2\_B, CT\_DATA\_1\_B, CT\_DATA\_0\_B: CHB data output termination control

$000 = 50\Omega$  (default)

$001 = 75\Omega$

$010 = 100\Omega$

$011 = 150\Omega$

$1xx = 300\Omega$

### Clock Divide/Data Format/Test Pattern (06h)

| BIT 7        | BIT 6     | BIT 5    | BIT 4    | BIT 3    | BIT 2     | BIT 1 | BIT 0 |

|--------------|-----------|----------|----------|----------|-----------|-------|-------|

| TEST_PATTERN | TEST_DATA | FORMAT_1 | FORMAT_0 | TERM_100 | SYNC_MODE | DIV1  | DIV0  |

Bit 7 TEST\_PATTERN: Test pattern selection

0 = Ramps from 0 to 255 (offset binary) and repeats (subsequent formatting applied) (default)

1 = Data alternates between D[7:0] = 01010101, DOR = 1, and D[7:0] = 10101010, DOR = 0 on both channels

Bit 6 TEST\_DATA: Data test mode

0 = Normal data output (default)

1 = Outputs test data pattern

Bit 5, 4 FORMAT\_1, FORMAT\_0: Data numerical format

00 = Two's complement (default)

01 = Offset binary

10 = Gray code

11 = Two's complement

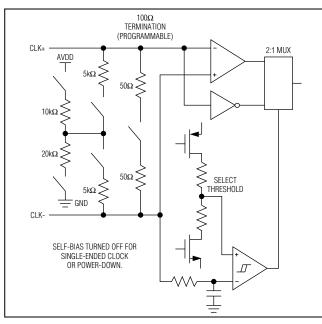

Bit 3 TERM\_100: Select  $100\Omega$  clock input termination

0 = No termination (default)

$1 = 100\Omega$  termination across differential clock inputs

Bit 2 SYNC\_MODE: Divider synchronization mode select

0 = Slip mode (Figure 11) (default)

1 = Edge mode (Figure 12)

Bit 1, 0 DIV1, DIV0: Input clock-divider select

00 = No divider (default)

01 = Divide-by-2

10 = Divide-by-4

11 = No divider

Reserved (07h)—Do not write to this register

### Common Mode (08h)

| BIT 7      | BIT 6       | BIT 5       | BIT 4       | BIT 3      | BIT 2       | BIT 1       | BIT 0       |

|------------|-------------|-------------|-------------|------------|-------------|-------------|-------------|

| CMI_SELF_B | CMI_ADJ_2_B | CMI_ADJ_1_B | CMI_ADJ_0_B | CMI_SELF_A | CMI_ADJ_2_A | CMI_ADJ_1_A | CMI_ADJ_0_A |

Bit 7 CMI\_SELF\_B: CHB connect input common-mode to analog inputs

0 = Internal common-mode voltage is NOT applied to inputs (default)

1 = Internal common-mode voltage applied to analog inputs through  $2k\Omega$  resistors

Bit 6, 5, 4 CMI\_ADJ\_2\_B, CMI\_ADJ\_1\_B, CMI\_ADJ\_0\_B: CHB input common-mode voltage adjustment

000 = 0.900V (default)

001 = 1.050V

010 = 1.200V

011 = 1.350V

100 = 0.900V

101 = 0.750V

110 = 0.600V

111 = 0.450V

Bit 3 CMI\_SELF\_A: CHA connect input common-mode to analog inputs

0 = Internal common-mode voltage is NOT applied to inputs (default)

1 = Internal common-mode voltage applied to analog inputs through  $2k\Omega$  resistors

Bit 2, 1, 0 CMI\_ADJ\_2\_A, CMI\_ADJ\_1\_A, CMI\_ADJ\_0\_A: CHA input common-mode adjustment

000 = 0.900V (default)

001 = 1.050V

010 = 1.200V

011 = 1.350V

100 = 0.900V

101 = 0.750V

110 = 0.600V

111 = 0.450V

## Software Reset (0Ah)

Bit 7–0 SWRESET: Write 5Ah to initiate software reset

Figure 8. Simplified Clock Input Schematic

#### **Clock Inputs**

The input clock interface provides for flexibility in the requirements of the clock driver. The MAX19507 accepts a fully differential clock or single-ended logic-level clock. For differential clock operation, connect a differential clock to the CLK+ and CLK- inputs. In this mode, the input common mode is established internally to allow for AC-coupling. The differential clock signal can also be DC-coupled if the common mode is constrained to the specified 1V to 1.4V clock input common-mode range. For single-ended operation, connect CLK- to GND and drive the CLK+ input with a logic-level signal. When the CLK- input is grounded (or pulled below the threshold of the clock mode detection comparator) the differential-to-single-ended conversion stage is disabled and the logic-level inverter path is activated.

### **Clock Divider**

The MAX19507 offers a clock-divider option. Enable clock division either by setting DIV0 and DIV1 through the serial interface; see the Clock Divide/Data

Figure 9. Dual-Bus Output Mode Timing

Figure 10. Multiplexed Output Mode Timing

Format/Test Pattern register (06h) for clock-d<u>ivider</u> options, or in parallel programming configuration (SPEN = 1) by using the DIV input.

#### **System Timing Requirements**

Figures 9 and 10 depict the relationship between the clock input and output, analog input, sampling event, and data output. The MAX19507 samples on the rising edge of the sampling clock. Output data is valid on the next rising edge of DCLK after a nine-clock internal latency. For applications where the clock is divided, the sample clock is the divided internal clock derived from:

[(CLK+ - CLK-)/DIVIDER]

#### Synchronization

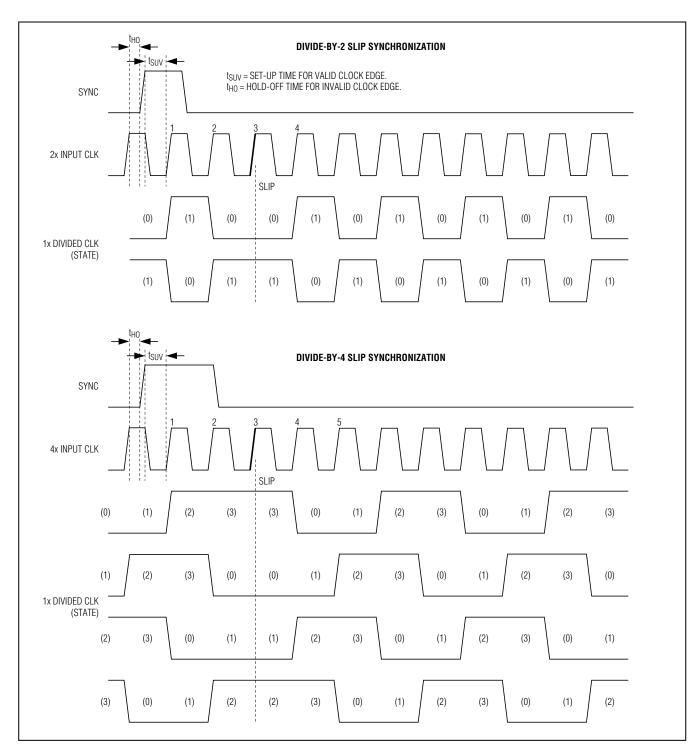

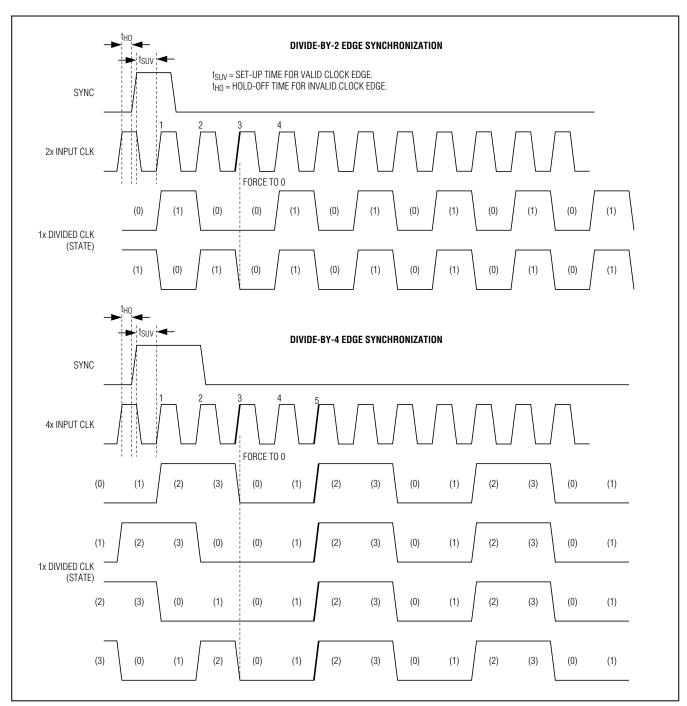

When using the clock divider, the phase of the internal clock can be different than that of the FPGA, microcontroller, or other MAX19507s in the system. There are two mechanisms to synchronize the internal clock: slip

synchronization and edge synchronization. Select the synchronization mode using SYNC\_MODE (bit 2) in the Clock Divide/Data Format/Test Pattern register (06h) and drive the SYNC input high to synchronize.

Slip Synchronization Mode, SYNC\_MODE = 0 (default): On the third rising edge of the input clock (CLK) after the rising edge of SYNC (provided set-up and hold times are met), the divided output is forced to skip a state transition (Figure 11).

Edge Synchronization Mode, SYNC\_MODE = 1: On the third rising edge of the input clock (CLK) after the rising edge of SYNC (provided set-up and hold times are met), the divided output is forced to state 0. A divided clock rising edge occurs on the fourth (/2 mode) or fifth (/4 mode) rising edge of CLK, after a valid rising edge of SYNC (Figure 12).

Figure 11. Slip Synchronization Mode

Figure 12. Edge Synchronization Mode

### **Table 4. Data Timing Controls**

| DATA TIMING CONTROL | DESCRIPTION                                                                                                                                                                                                       |