### **General Description**

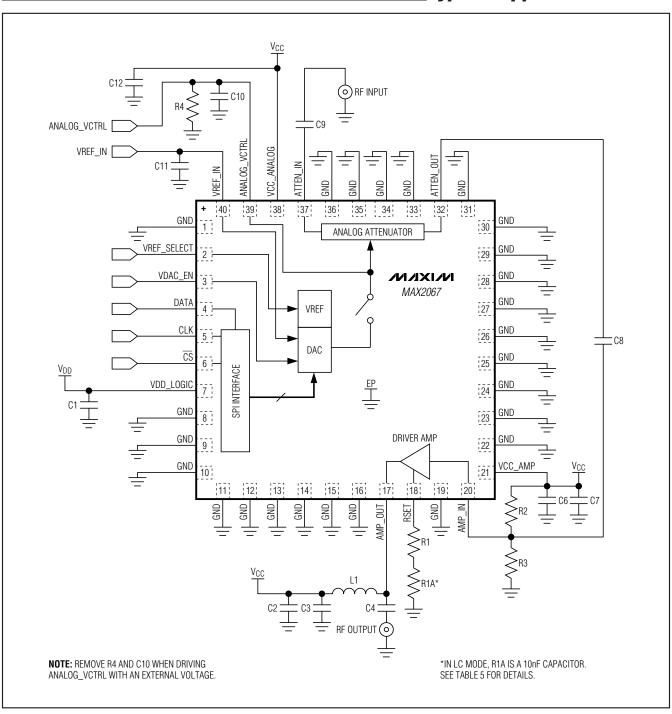

The MAX2067 high-linearity analog variable-gain amplifier (VGA) is a monolithic SiGe BiCMOS attenuator and amplifier designed to interface with  $50\Omega$  systems operating in the 50MHz to 1000MHz frequency range (see the Typical Application Circuit). The analog attenuator is controlled using an external voltage or through the SPI™-compatible interface using an on-chip 8-bit DAC.

Because each stage has its own RF input and RF output, this component can be configured to either optimize NF (amplifier configured first), or OIP3 (amplifier last). The device's performance features include 22dB amplifier gain (amplifier only), 4dB NF at maximum gain (includes attenuator insertion loss), and a high OIP3 level of +43dBm. Each of these features makes the MAX2067 an ideal VGA for numerous receiver and transmitter applications.

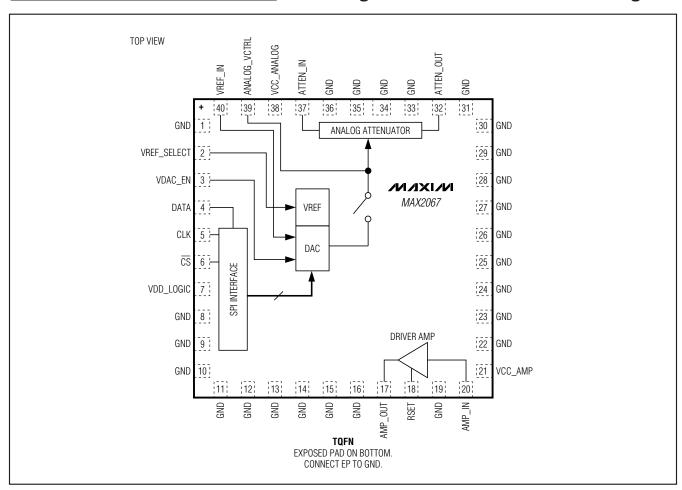

In addition, the MAX2067 operates from a single +5V supply with full performance, or a single +3.3V supply with slightly reduced performance, and has an adjustable bias to trade current consumption for linearity performance. This device is available in a compact 40pin thin QFN package (6mm x 6mm) with an exposed pad. Electrical performance is guaranteed over the extended temperature range ( $T_C = -40$ °C to +85°C).

#### **Applications**

IF and RF Gain Stages

Temperature Compensation Circuits

Cellular Band WCDMA and cdma2000® Base Stations

GSM 850/GSM 900 EDGE Base Stations

WiMAX and LTE Base Stations and Customer Premise Equipment

Fixed Broadband Wireless Access

Wireless Local Loop

Military Systems

Video-on-Demand (VOD) and DOCSIS®-Compliant EDGE QAM Modulation

Cable Modem Termination Systems (CMTS)

RFID Handheld and Portal Readers

#### **Features**

- ♦ 50MHz to 1000MHz RF Frequency Range

- **♦ Pin-Compatible Family Includes** MAX2065 (Analog/Digital VGA) MAX2066 (Digital VGA)

- ♦ +21.9dB (typ) Maximum Gain

- ♦ 0.5dB Gain Flatness Over 100MHz Bandwidth

- ♦ 31dB Gain Range

- ♦ Built-In DAC for Analog Attenuation Control

- **♦** Excellent Linearity (Configured with Amplifier Last)

- +43dBm OIP3

- +66dBm OIP2

- +19dBm Output 1dB Compression Point

- -70dBc HD2

- -87dBc HD3

- ♦ 4dB Typical Noise Figure (NF)

- ♦ Single +5V Supply (Optional +3.3V Operation)

- ♦ External Current-Setting Resistors Provide Option for Operating Device in Reduced-Power/ **Reduced-Performance Mode**

#### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE     |

|--------------|----------------|-----------------|

| MAX2067ETL+  | -40°C to +85°C | 40 Thin QFN-EP* |

| MAX2067ETL+T | -40°C to +85°C | 40 Thin QFN-EP* |

<sup>+</sup>Denotes a lead-free package.

#### Pin Configuration appears at end of data sheet.

SPI is a trademark of Motorola, Inc.

cdma2000 is a registered trademark of Telecommunications Industry Association.

DOCSIS and CableLabs are registered trademarks of Cable Television Laboratories, Inc. (CableLabs®).

<sup>\*</sup>EP = Exposed pad.

T = Tape and reel.

#### **ABSOLUTE MAXIMUM RATINGS**

| VCC_ to GND                                | RF Input Power (AMP_IN)                 |

|--------------------------------------------|-----------------------------------------|

| RF Input Power (ATTEN_IN, ATTEN_OUT)+20dBm | Lead Temperature (soldering, 10s)+300°C |

- Note 1: Based on junction temperature T<sub>J</sub> = T<sub>C</sub> + (θ<sub>JC</sub> x V<sub>CC</sub> x I<sub>CC</sub>). This formula can be used when the temperature of the exposed pad is known while the device is soldered down to a printed-circuit board (PCB). See the *Applications Information* section for details. The junction temperature must not exceed +150°C.

- **Note 2:** Junction temperature  $T_J = T_A + (\theta_{JA} \times V_{CC} \times I_{CC})$ . This formula can be used when the ambient temperature of the PCB is known. The junction temperature must not exceed +150°C.

- **Note 3:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a 4-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

- Note 4: T<sub>C</sub> is the temperature on the exposed pad of the package. T<sub>A</sub> is the ambient temperature of the device and PCB.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### +3.3V SUPPLY DC ELECTRICAL CHARACTERISTICS

(Typical Application Circuit, high-current (HC) mode,  $V_{CC} = V_{DD} = +3.0V$  to +3.6V,  $T_{C} = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $V_{CC} = V_{DD} = +3.3V$  and  $T_{C} = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                          | SYMBOL          | CONDITIONS | MIN | TYP | MAX | UNITS |  |

|----------------------------------------------------|-----------------|------------|-----|-----|-----|-------|--|

| Supply Voltage                                     | Vcc             | Note 5     | 3.0 | 3.3 | 3.6 | V     |  |

| Supply Current                                     | Icc             |            |     | 60  | 82  | mA    |  |

| LOGIC INPUTS (DATA, CS, CLK, VDAC_EN, VREF_SELECT) |                 |            |     |     |     |       |  |

| Input High Voltage                                 | VIH             |            |     | 2   |     | V     |  |

| Input Low Voltage                                  | V <sub>IL</sub> |            |     | 0.8 |     | V     |  |

#### +5V SUPPLY DC ELECTRICAL CHARACTERISTICS

(Typical Application Circuit,  $V_{CC} = V_{DD} = +4.75V$  to +5.25V,  $T_{C} = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $V_{CC} = V_{DD} = +5V$  and  $T_{C} = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                    | SYMBOL     | CONDITIONS             | MIN  | TYP | MAX  | UNITS |

|------------------------------|------------|------------------------|------|-----|------|-------|

| Supply Voltage               | Vcc        |                        | 4.75 | 5   | 5.25 | V     |

| Constant Constant            | la a       | Low-current (LC) mode  |      | 72  | 92   | Λ     |

| Supply Current               | Icc        | High-current (HC) mode |      | 123 | 146  | mA    |

| LOGIC INPUTS (DATA, CS, CLK, | VDAC_EN, V | /REF_SELECT)           |      |     |      |       |

| Input High Voltage           | VIH        |                        | 3    |     |      | V     |

| Input Low Voltage            | VIL        |                        |      |     | 8.0  | V     |

| Input Current Logic-High     | lін        |                        | -1   |     | +1   | μΑ    |

| Input Current Logic-Low      | IIL        |                        | -1   |     | +1   | μΑ    |

#### +3.3V SUPPLY AC ELECTRICAL CHARACTERISTICS

(*Typical Application Circuit*,  $V_{CC} = V_{DD} = +3.0 \text{V}$  to +3.6 V,  $T_{C} = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ . Typical values are at  $V_{CC} = V_{DD} = +3.3 \text{V}$ , HC mode with attenuator set for maximum gain,  $P_{IN} = -200 \text{Bm}$ ,  $f_{RF} = 200 \text{MHz}$ , and  $T_{C} = +25 ^{\circ}\text{C}$ , unless otherwise noted.) (Note 6)

| PARAMETER                             | SYMBOL | CONDITIONS                                         | MIN | TYP  | MAX  | UNITS |

|---------------------------------------|--------|----------------------------------------------------|-----|------|------|-------|

| RF Frequency Range                    | fRF    | (Notes 5, 7)                                       | 50  |      | 1000 | MHz   |

| Small-Signal Gain                     | G      |                                                    |     | 21.3 |      | dB    |

| Output Third-Order Intercept<br>Point | OIP3   | P <sub>OUT</sub> = 0dBm/tone, maximum gain setting |     | 38   |      | dBm   |

| Noise Figure                          | NF     | Maximum gain setting                               |     | 4.3  |      | dB    |

| Total Attenuation Range               |        |                                                    |     | 31   |      | dB    |

#### +5V SUPPLY AC ELECTRICAL CHARACTERISTICS

(*Typical Application Circuit*,  $V_{CC} = V_{DD} = +4.75$  to +5.25V, HC mode with attenuator set for maximum gain,  $50MHz \le f_{RF} \le 1000MHz$ ,  $T_{C} = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $V_{CC} = V_{DD} = +5.0V$ , HC mode,  $P_{IN} = -20dBm$ ,  $f_{RF} = 200MHz$ , and  $T_{C} = +25^{\circ}C$ , unless otherwise noted.) (Note 6)

| PARAMETER                              | SYMBOL          | COND                                                 | ITIONS                | MIN  | TYP    | MAX  | UNITS |

|----------------------------------------|-----------------|------------------------------------------------------|-----------------------|------|--------|------|-------|

| RF Frequency Range                     | f <sub>RF</sub> | (Notes 5, 7)                                         |                       | 50   |        | 1000 | MHz   |

|                                        |                 | 200MHz                                               |                       |      | 21.9   |      |       |

|                                        |                 | 350MHz, T <sub>C</sub> = +25°C                       | (Note 5)              | 20.3 | 21.3   | 22.3 |       |

| Small-Signal Gain                      | G               | 450MHz                                               |                       |      | 20.9   |      | dB    |

|                                        |                 | 750MHz                                               |                       |      | 19.4   |      |       |

|                                        |                 | 900MHz                                               |                       |      | 18.7   |      |       |

| Gain Variation vs. Temperature         |                 |                                                      |                       |      | -0.006 |      | dB/°C |

| Gain Flatness vs. Frequency            |                 | Any 100MHz frequence to 500MHz                       | cy band from 50MHz    |      | 0.5    |      | dB    |

|                                        |                 | 200MHz                                               |                       |      | 4      |      |       |

|                                        |                 | 350MHz, T <sub>C</sub> = +25°C (Note 5)              |                       |      | 4.2    | 5.2  | dB    |

| Noise Figure                           | NF              | 450MHz                                               |                       |      | 4.3    |      |       |

|                                        |                 | 750MHz                                               |                       |      | 4.8    |      |       |

|                                        |                 | 900MHz                                               |                       |      | 5      |      |       |

| Total Attenuation Range                |                 |                                                      |                       |      | 31     |      | dB    |

| Output Second-Order Intercept<br>Point | OIP2            | $P_{OUT} = 0dBm/tone, \Delta$                        | $f = 1MHz, f_1 + f_2$ |      | 66     |      | dBm   |

|                                        |                 |                                                      | 200MHz                |      | 43     |      |       |

|                                        |                 | D 0.1D #                                             | 350MHz                |      | 40.8   |      |       |

|                                        |                 | $P_{OUT} = 0dBm/tone,$<br>HC mode, $\Delta f = 1MHz$ | 450MHz                |      | 39.8   |      |       |

| Output Third-Order Intercept<br>Point  |                 |                                                      | 750MHz                |      | 37.3   |      | dBm   |

|                                        | OIP3            |                                                      | 900MHz                |      | 36.2   |      |       |

|                                        | Oii 3           |                                                      | 200MHz                |      | 40     |      |       |

|                                        |                 | Dour OdDm/tono                                       | 350MHz                |      | 38.2   |      |       |

|                                        |                 | $P_{OUT} = 0dBm/tone,$<br>LC mode, $\Delta f = 1MHz$ | 450MHz                |      | 37.4   |      |       |

|                                        |                 |                                                      | 750MHz                |      | 35.5   |      |       |

|                                        |                 |                                                      | 900MHz                |      | 34.3   |      |       |

### +5V SUPPLY AC ELECTRICAL CHARACTERISTICS (continued)

(*Typical Application Circuit*,  $V_{CC} = V_{DD} = +4.75$  to +5.25V, HC mode with attenuator set for maximum gain,  $50MHz \le f_{RF} \le 1000MHz$ ,  $T_{C} = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $V_{CC} = V_{DD} = +5.0V$ , HC mode,  $P_{IN} = -20dBm$ ,  $f_{RF} = 200MHz$ , and  $T_{C} = +25^{\circ}C$ , unless otherwise noted.) (Note 6)

| PARAMETER                             | SYMBOL           | CONDITIONS                                                                                 | MIN  | TYP   | MAX  | UNITS   |

|---------------------------------------|------------------|--------------------------------------------------------------------------------------------|------|-------|------|---------|

| Output -1dB Compression Point         | P <sub>1dB</sub> | 350MHz, T <sub>C</sub> = +25°C (Notes 5, 8)                                                | 17   | 18.7  |      | dBm     |

| Second Harmonic                       |                  | $P_{OUT}$ = +3dBm, $f_{RF}$ = 200MHz, $T_{C}$ = +25°C (Note 5)                             | -61  | -70   |      | dBc     |

| Third Harmonic                        |                  | $P_{OUT}$ = +3dBm, $f_{RF}$ = 200MHz, $T_{C}$ = +25°C (Note 5)                             | -74  | -87   |      | dBc     |

| Attenuator Response Time              |                  | Input from ANALOG_VCTRL                                                                    |      | 1     |      |         |

| (Note 9)                              |                  | Input from CS rising edge                                                                  |      | 3.2   |      | μs      |

| Group Delay                           |                  | Maximum gain setting, includes EV kit PCB delays                                           |      | 0.8   |      | ns      |

| Input Return Loss                     |                  | $50\Omega$ source, maximum gain setting                                                    |      | 30    |      | dB      |

| Output Return Loss                    |                  | $50\Omega$ load, maximum gain setting                                                      |      | 16    |      | dB      |

| ANALOG ATTENUATOR                     |                  |                                                                                            |      |       |      |         |

| Insertion Loss                        |                  |                                                                                            |      | 1.2   |      | dB      |

| Input Second-Order Intercept<br>Point | IIP2             | $P_{RF1}$ = 0dBm, $P_{RF2}$ = 0dBm, maximum gain setting, $\Delta f$ = 1MHz, $f_1$ + $f_2$ |      | 70    |      | dBm     |

| Input Third-Order Intercept Point     | IIP3             | P <sub>RF1</sub> = 0dBm, P <sub>RF2</sub> = 0dBm, maximum gain setting, Δf = 1MHz          |      | 36    |      | dBm     |

| Attenuation Range                     |                  | Analog control input                                                                       |      | 31    |      | dB      |

| Gain-Control Slope                    |                  | Analog control input                                                                       |      | -12.5 |      | dB/V    |

| Maximum Gain-Control Slope            |                  | Over analog control input range                                                            |      | -35   |      | dB/V    |

| Insertion Phase Change                |                  | Over analog control input range                                                            |      | 18    |      | Degrees |

| Group Delay vs. Control Voltage       |                  | Over analog control input range                                                            |      | -0.25 |      | ns      |

| Analog Control Input Range            |                  |                                                                                            | 0.25 |       | 2.75 | V       |

| Analog Control Input Impedance        |                  |                                                                                            |      | 80    |      | kΩ      |

| Input Return Loss                     |                  | $50\Omega$ source, maximum gain setting                                                    |      | 22    |      | dB      |

| Output Return Loss                    |                  | $50\Omega$ load, maximum gain setting                                                      |      | 22    |      | dB      |

| DAC                                   |                  |                                                                                            |      |       |      |         |

| Number of Bits                        |                  |                                                                                            |      | 8     |      | Bits    |

| Output Voltage                        |                  | DAC code = 00000000                                                                        |      |       | 0.25 |         |

| Carpar Vollage                        |                  | DAC code = 11111111                                                                        | 2.75 |       |      | v       |

NIXIN

#### +5V SUPPLY AC ELECTRICAL CHARACTERISTICS (continued)

(*Typical Application Circuit*,  $V_{CC} = V_{DD} = +4.75$  to +5.25V, HC mode with attenuator set for maximum gain, 50MHz  $\leq$  f<sub>RF</sub>  $\leq$  1000MHz,  $T_{C} = -40^{\circ}$ C to  $+85^{\circ}$ C. Typical values are at  $V_{CC} = V_{DD} = +5.0$ V, HC mode,  $P_{IN} = -20$ dBm, f<sub>RF</sub> = 200MHz, and  $T_{C} = +25^{\circ}$ C, unless otherwise noted.) (Note 6)

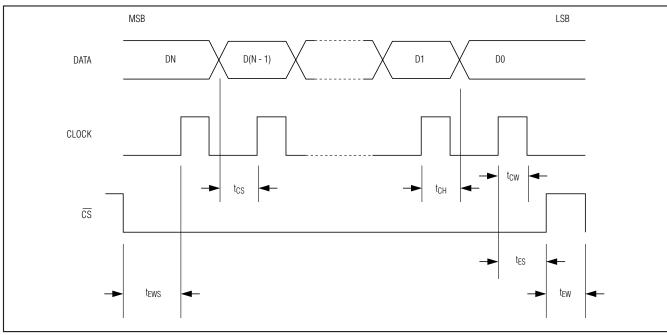

| PARAMETER                         | SYMBOL          | CONDITIONS | MIN | TYP | MAX | UNITS |  |

|-----------------------------------|-----------------|------------|-----|-----|-----|-------|--|

| SERIAL PERIPHERAL INTERFACE (SPI) |                 |            |     |     |     |       |  |

| Maximum Clock Speed               | fCLK            |            |     | 20  |     | MHz   |  |

| Data-to-Clock Setup Time          | tcs             |            |     | 2   |     | ns    |  |

| Data-to-Clock Hold Time           | tсн             |            |     | 2.5 |     | ns    |  |

| Clock-to-CS Setup Time            | tES             |            |     | 3   |     | ns    |  |

| CS Positive Pulse Width           | t <sub>EW</sub> |            |     | 7   |     | ns    |  |

| CS Setup Time                     | tews            |            |     | 3.5 |     | ns    |  |

| Clock Pulse Width                 | tcw             | ·          |     | 5   |     | ns    |  |

- Note 5: Guaranteed by design and characterization.

- Note 6: All limits include external component losses. Output measurements are performed at RF output port of the *Typical Application Circuit*

- Note 7: Operating outside this range is possible, but with degraded performance of some parameters.

- Note 8: It is advisable not to continuously operate the VGA RF input above +15dBm.

- Note 9: Response time includes full attenuation range change with output setting to within ±0.1dB.

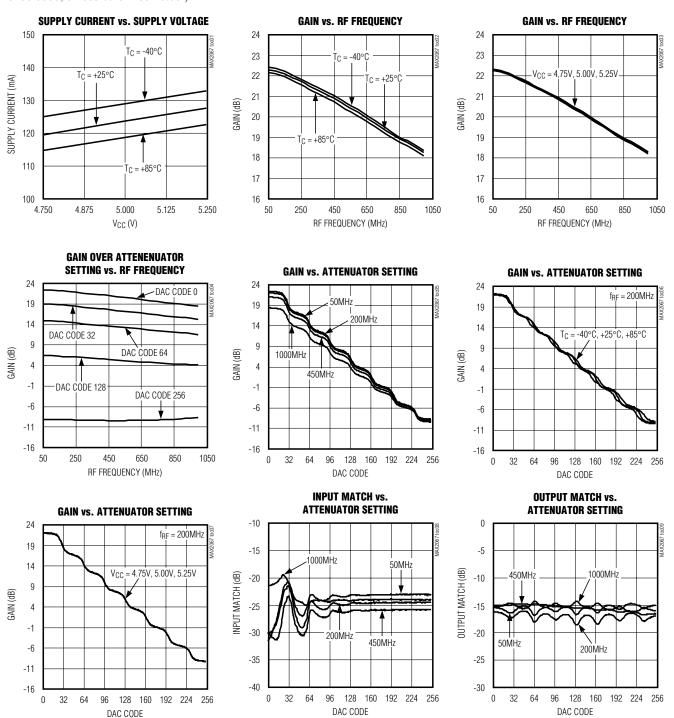

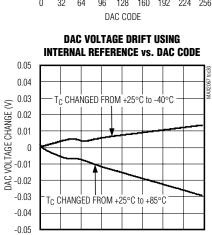

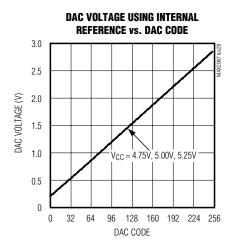

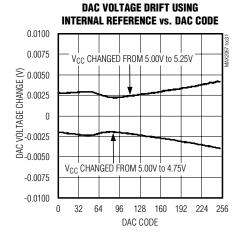

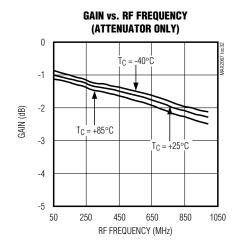

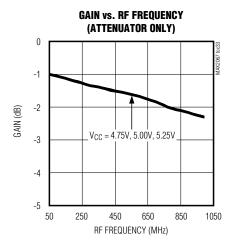

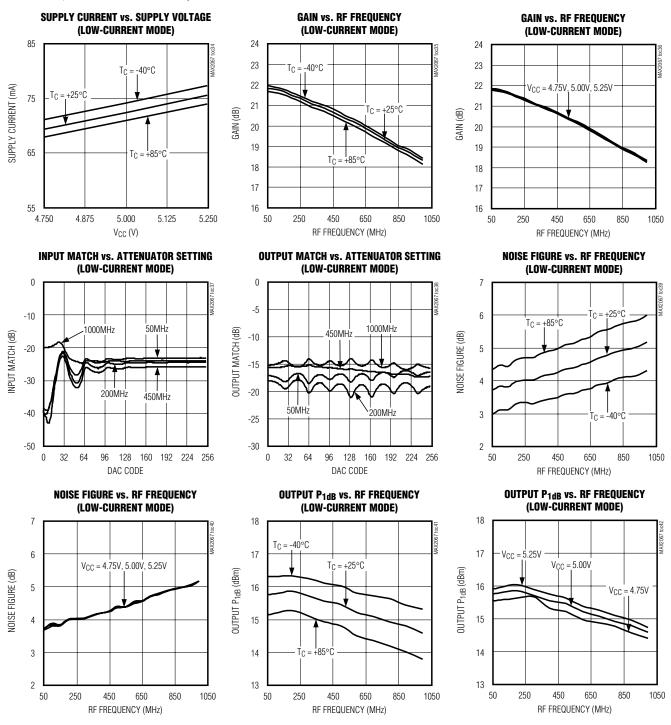

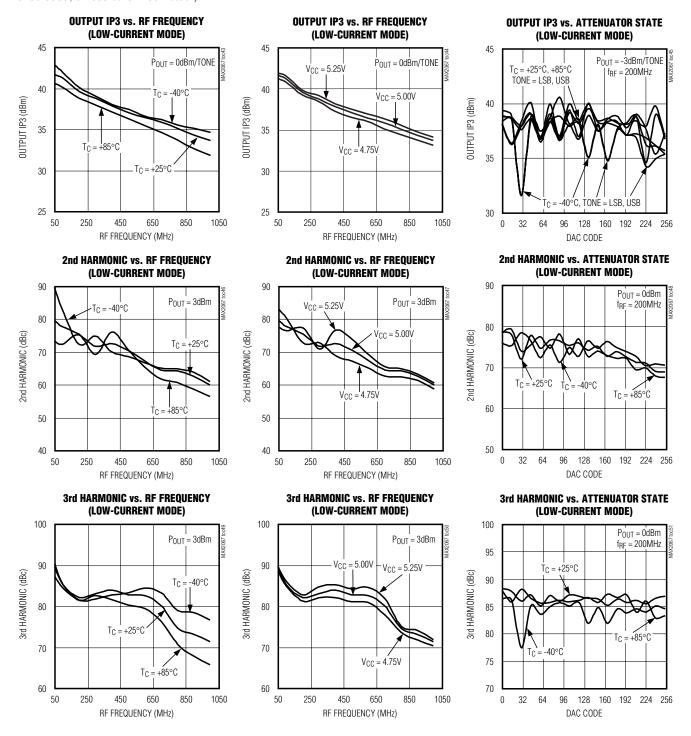

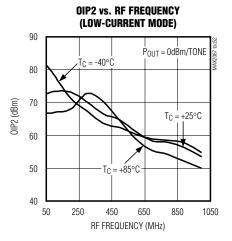

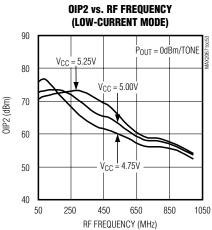

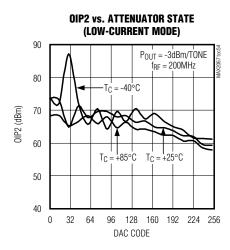

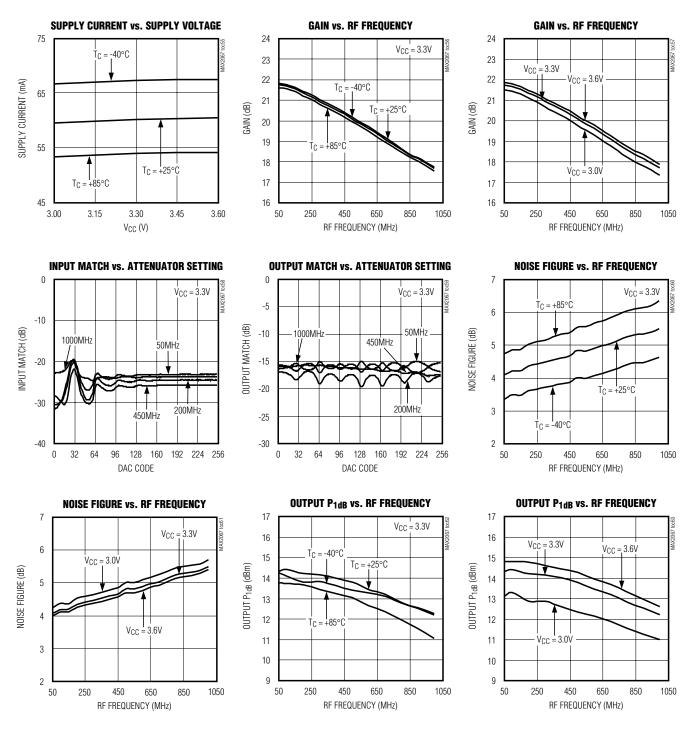

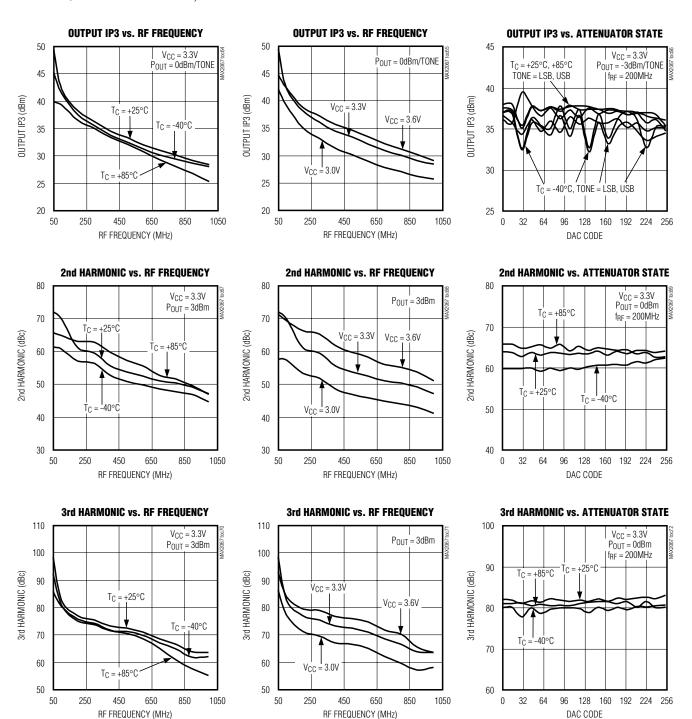

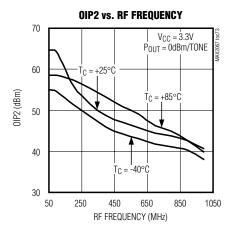

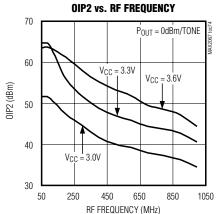

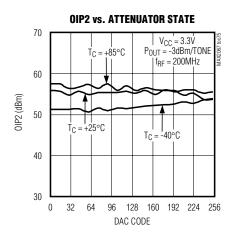

### Typical Operating Characteristics

( $V_{CC} = V_{DD} = +5.0V$ , HC mode, attenuator set for maximum gain,  $P_{IN} = -20$ dBm,  $f_{RF} = 200$ MHz, and  $T_{C} = +25$ °C, internal DAC reference used, unless otherwise noted.)

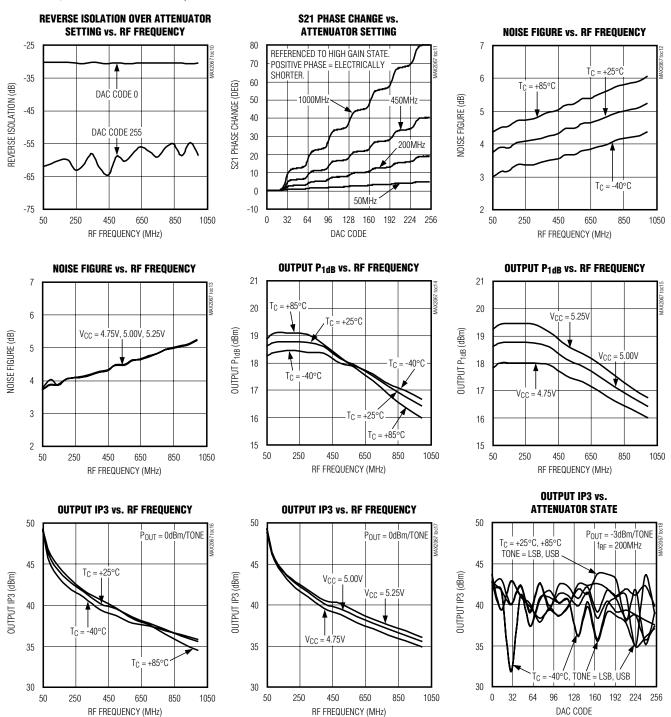

### Typical Operating Characteristics (continued)

( $V_{CC} = V_{DD} = +5.0V$ , HC mode, attenuator set for maximum gain,  $P_{IN} = -20$ dBm,  $f_{RF} = 200$ MHz, and  $T_{C} = +25$ °C, internal DAC reference used, unless otherwise noted.)

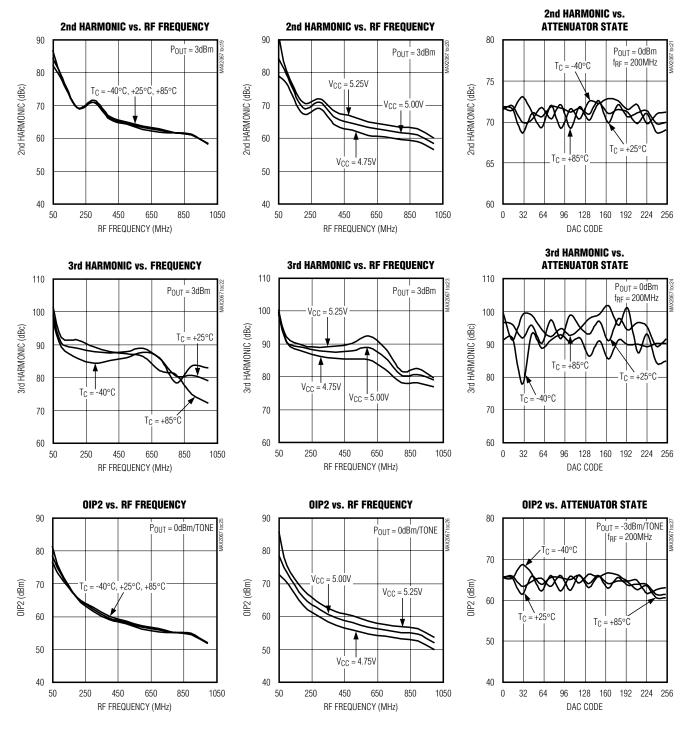

### Typical Operating Characteristics (continued)

( $V_{CC} = V_{DD} = +5.0V$ , HC mode, attenuator set for maximum gain,  $P_{IN} = -20$ dBm,  $f_{RF} = 200$ MHz, and  $T_{C} = +25$ °C, internal DAC reference used, unless otherwise noted.)

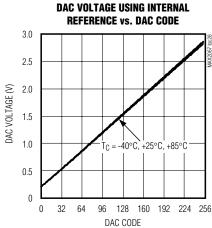

### Typical Operating Characteristics (continued)

( $V_{CC} = V_{DD} = +5.0V$ , HC mode, attenuator set for maximum gain,  $P_{IN} = -20 \text{dBm}$ ,  $f_{RF} = 200 \text{MHz}$ , and  $T_{C} = +25 ^{\circ}\text{C}$ , internal DAC reference used, unless otherwise noted.)

96 128 160 192 224 256

DAC CODE

0 32

### Typical Operating Characteristics (continued)

( $V_{CC} = V_{DD} = +5.0V$ , attenuator only, maximum gain,  $P_{IN} = -20$ dBm, and  $T_{C} = +25$ °C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

( $V_{CC} = V_{DD} = +5.0V$ , LC mode, attenuator set for maximum gain,  $P_{IN} = -20$ dBm,  $f_{RF} = 200$ MHz, and  $T_{C} = +25$ °C, internal DAC reference used, unless otherwise noted.)

### Typical Operating Characteristics (continued)

( $V_{CC} = V_{DD} = +5.0V$ , LC mode, attenuator set for maximum gain,  $P_{IN} = -20$ dBm,  $f_{RF} = 200$ MHz, and  $T_{C} = +25$ °C, internal DAC reference used, unless otherwise noted.)

### Typical Operating Characteristics (continued)

( $V_{CC} = V_{DD} = +5.0V$ , LC mode, attenuator set for maximum gain,  $P_{IN} = -20$ dBm,  $f_{RF} = 200$ MHz, and  $T_{C} = +25$ °C, internal DAC reference used, unless otherwise noted.)

### Typical Operating Characteristics (continued)

( $V_{CC} = V_{DD} = +3.3V$ , HC mode, attenuator set for maximum gain,  $P_{IN} = -20$ dBm,  $f_{RF} = 200$ MHz, and  $T_{C} = +25$ °C, internal DAC reference used, unless otherwise noted.)

### Typical Operating Characteristics (continued)

( $V_{CC} = V_{DD} = +3.3V$ , HC mode, attenuator set for maximum gain,  $P_{IN} = -20$ dBm,  $f_{RF} = 200$ MHz, and  $T_{C} = +25$ °C, internal DAC reference used, unless otherwise noted.)

### Typical Operating Characteristics (continued)

( $V_{CC} = V_{DD} = +3.3V$ , HC mode, attenuator set for maximum gain,  $P_{IN} = -20$ dBm,  $f_{RF} = 200$ MHz, and  $T_{C} = +25$ °C, internal DAC reference used, unless otherwise noted.)

## Pin Description

| PIN                                 | NAME         | DESCRIPTION                                                                                                                                                                                                             |  |  |

|-------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 16, 19, 22, 24–28, 30, 31, 33–36 | GND          | Ground                                                                                                                                                                                                                  |  |  |

| 2                                   | VREF_SELECT  | DAC Reference Voltage Selection Logic Input. Logic 1 = internal DAC reference voltage, Logic 0 = external DAC reference voltage. Logic input disabled (don't care) when VDAC_EN = Logic 0.                              |  |  |

| 3                                   | VDAC_EN      | DAC Enable/Disable Logic Input. Logic 0 = disable DAC circuit, Logic 1 = enable DAC circuit.                                                                                                                            |  |  |

| 4                                   | DATA         | SPI Data Digital Input                                                                                                                                                                                                  |  |  |

| 5                                   | CLK          | SPI Clock Digital Input                                                                                                                                                                                                 |  |  |

| 6                                   | CS           | SPI Chip-Select Digital Input                                                                                                                                                                                           |  |  |

| 7                                   | VDD_LOGIC    | Digital Logic Supply Input. Connect to the digital logic power supply, V <sub>DD</sub> , Bypass to GND with a 10nF capacitor as close as possible to the pin.                                                           |  |  |

| 8–15, 23, 29                        | GND          | Ground. See the <i>Pin-Compatibility Considerations</i> section.                                                                                                                                                        |  |  |

| 17                                  | AMP_OUT      | Driver Amplifier Output (50 $\Omega$ ). See the <i>Typical Application Circuit</i> for details.                                                                                                                         |  |  |

| 18                                  | RSET         | Driver Amplifier Bias-Setting Input. See the External Bias section.                                                                                                                                                     |  |  |

| 20                                  | AMP_IN       | Driver Amplifier Input (50Ω). See the <i>Typical Application Circuit</i> for details.                                                                                                                                   |  |  |

| 21                                  | VCC_AMP      | Driver Amplifier Supply Voltage Input. Connect to the V <sub>CC</sub> power supply. Bypass to GND with 1000pF and 10nF capacitors as close as possible to the pin, with the smaller value capacitor closer to the part. |  |  |

| 32                                  | ATTEN_OUT    | Analog Attenuator Output. Internally matched to $50\Omega$ . Requires an external DC-blocking capacitor.                                                                                                                |  |  |

| 37                                  | ATTEN_IN     | Analog Attenuator Input. Internally matched to $50\Omega$ . Requires an external DC-blocking capacitor.                                                                                                                 |  |  |

| 38                                  | VCC_ANALOG   | Analog Bias and Control Supply Voltage Input. Bypass to GND with a 10nF capacitor as close as possible to the pin.                                                                                                      |  |  |

| 39                                  | ANALOG_VCTRL | Analog Attenuator Voltage-Control Input                                                                                                                                                                                 |  |  |

| 40                                  | VREF_IN      | External DAC Voltage Reference Input                                                                                                                                                                                    |  |  |

| _                                   | EP           | Exposed Pad. Internally connected to GND. Connect EP to ground for proper RF performance and enhanced thermal dissipation.                                                                                              |  |  |

### **Detailed Description**

The MAX2067 high-linearity analog variable-gain amplifier is a general-purpose, high-performance amplifier designed to interface with  $50\Omega$  systems operating in the 50MHz to 1000MHz frequency range.

The MAX2067 integrates an analog attenuator to provide 31dB of total gain control, as well as a driver amplifier optimized to provide high gain, high IP3, low noise figure, and low power consumption. For applications that do not require high linearity, the bias current of the amplifier can be adjusted by an external resistor to further reduce power consumption.

The analog attenuator is controlled using an external voltage or through the SPI-compatible interface using an on-chip DAC. Because each stage has its own external RF input and RF output, this component can be configured to either optimize NF (amplifier configured first), or OIP3 (amplifier last). The device's performance features include 22dB stand-alone amplifier gain (amplifier only), 4dB NF at maximum gain (includes attenuator insertion loss), and a high OIP3 level of +43dBm. Each of these features makes the MAX2067 an ideal VGA for numerous receiver and transmitter applications.

In addition, the MAX2067 operates from a single +5V supply, or a single +3.3V supply with slightly reduced performance, and has adjustable bias to trade current consumption for linearity performance.

#### **Analog Attenuator**

The MAX2067's analog attenuator has a dynamic range of 31dB and is controlled using an external voltage or through the 3-wire SPI using an on-chip 8-bit DAC. See the *Applications Information* section and Table 1 for attenuator programming details. The attenuator can be used for both static and dynamic power control.

#### **Driver Amplifier**

The MAX2067 includes a high-performance driver with a fixed gain of 22dB. The driver amplifier circuit is optimized for high linearity for the 50MHz to 1000MHz frequency range.

### **Applications Information**

#### **Attenuator Control**

The analog attenuator is controlled by either an external control voltage applied at ANALOG\_VCTRL (pin 39) or by the on-chip 8-bit DAC. Through the utilization of this control DAC, the user can easily adjust the analog attenuation in 0.12dB increments through a simple SPI command. The DAC enable/disable logic-input pin (VDAC\_EN), and the DAC reference voltage selection logic-input pin (VREF\_SELECT) determine how the attenuator is controlled. When the DAC is enabled, either the on-chip voltage reference or the external voltage reference can be selected. See Table 1 for the attenuator and DAC operation truth table.

Although this on-chip DAC eliminates the need for an external analog control voltage, the user still has the option of disabling the DAC and using an external analog control voltage for instances where additional attenuation resolution is needed, or in cases where the gain trim/automatic gain-control (AGC) loop is purely analog.

#### **SPI Interface and Attenuator Settings**

The MAX2067 employs a 3-wire SPI/MICROWIRETM-compatible serial interface to program the on-chip DAC. Eight bits of data are shifted in MSB first and framed by CS. When CS is low, the clock is active and data is shifted on the rising edge of the clock. When CS transitions high, the data is latched and the attenuator setting changes (Figure 1). See Table 2 for details on the SPI data format.

**Table 1. Control Logic**

| VDAC_EN | VREF_SELECT | ANALOG ATTENUATOR                      | D/A CONVERTER                                 |

|---------|-------------|----------------------------------------|-----------------------------------------------|

| 0       | X           | Controlled by external control voltage | Disabled                                      |

| 1       | 1           | Controlled by on-chip DAC              | Enabled (DAC uses on-chip voltage reference)  |

| 1       | 0           | Controlled by on-chip DAC              | Enabled (DAC uses external voltage reference) |

X = Don't care.

MICROWIRE is a trademark of National Semiconductor Corp.

Figure 1. SPI Timing Diagram

#### **Table 2. SPI Data Format**

| FUNCTION    | BIT      | DESCRIPTION                                                      |  |  |  |

|-------------|----------|------------------------------------------------------------------|--|--|--|

|             | D7       | Bit 7 (MSB) of on-chip DAC used to program the analog attenuator |  |  |  |

|             | D6       | Bit 6 of DAC                                                     |  |  |  |

|             | D5       | Bit 5 of DAC                                                     |  |  |  |

| On Chin DAC | D4       | Bit 4 of DAC                                                     |  |  |  |

| On-Chip DAC | D3       | Bit 3 of DAC                                                     |  |  |  |

|             | D2       | Bit 2 of DAC                                                     |  |  |  |

| D1          |          | Bit 1 of DAC                                                     |  |  |  |

|             | D0 (LSB) | Bit 0 (LSB) of the on-chip DAC                                   |  |  |  |

#### **External Bias**

Bias currents for the driver amplifier are set and optimized through external resistors. Resistors R1 and R1A connected to RSET (pin 18) set the bias current for the amplifier. The external biasing resistor values can be increased for reduced current operation at the expense of performance. See Tables 4 and 5 for details.

#### **Pin-Compatibility Considerations**

The MAX2067 is a simplified version of the MAX2065 analog/digital VGA. The MAX2067 does not contain a digital attenuator and parallel inputs D0–D4. The associated input/output pins are internally connected to ground (Table 3). Ground the unused input/output pins to optimize isolation. (See the *Typical Application Circuit.*)

#### +5V and +3.3V Supply Voltage

The MAX2067 features an optional +3.3V supply voltage operation with slightly reduced linearity performance.

#### **Layout Considerations**

The pin configuration of the MAX2067 has been optimized to facilitate a very compact physical layout of the device and its associated discrete components.

The exposed paddle (EP) of the MAX2067's 40-pin thin QFN-EP package provides a low thermal-resistance path to the die. It is important that the PCB on which the MAX2067 is mounted be designed to conduct heat from the EP. In addition, provide the EP with a low-inductance path to electrical ground. The EP **must** be soldered to a ground plane on the PCB, either directly or through an array of plated via holes.

Table 3. MAX2065/MAX2067 Pin Comparison

| PIN | MAX2065    | MAX2067 |

|-----|------------|---------|

| 8   | SER/PAR    | GND     |

| 9   | STATE_A    | GND     |

| 10  | STATE_B    | GND     |

| 11  | D4         | GND     |

| 12  | D3         | GND     |

| 13  | D2         | GND     |

| 14  | D1         | GND     |

| 15  | D0         | GND     |

| 23  | ATTEN2_OUT | GND     |

| 29  | ATTEN2_IN  | GND     |

**Table 4. Typical Application Circuit Component Values (HC Mode)**

| DESIGNATION                                       | VALUE  | SIZE                              | VENDOR                          | DESCRIPTION            |

|---------------------------------------------------|--------|-----------------------------------|---------------------------------|------------------------|

| C1, C2, C7, C12                                   | 10nF   | 0402                              | Murata Mfg. Co., Ltd.           | X7R                    |

| C3, C4, C6, C8, C9                                | 1000pF | 0402                              | Murata Mfg. Co., Ltd.           | C0G ceramic capacitors |

| C10, C11                                          | 150pF  | 0402                              | Murata Mfg. Co., Ltd.           | C0G ceramic capacitors |

| L1                                                | 470nH  | 1008                              | Coilcraft, Inc.                 | 1008CS-471XJLC         |

| R1, R1A                                           | 10Ω    | 0402                              | Panasonic Corp.                 | 1%                     |

| R2 (+3.3V applications only)                      | 1kΩ    | 0402                              | Panasonic Corp.                 | 1%                     |

| R3 (+3.3V applications only)                      | 2kΩ    | 0402                              | Panasonic Corp.                 | 1%                     |

| R4 (+5V applications and using internal DAC only) | 47kΩ   | 0402                              | Panasonic Corp.                 | 1%                     |

| U1                                                | _      | 40-pin thin QFN-EP<br>(6mm x 6mm) | Maxim Integrated Products, Inc. | MAX2067ETL+            |

**Table 5. Typical Application Circuit Component Values (LC Mode)**

| DESIGNATION                                       | VALUE  | SIZE                              | VENDOR                          | DESCRIPTION            |

|---------------------------------------------------|--------|-----------------------------------|---------------------------------|------------------------|

| C1, C2, C7, C12                                   | 10nF   | 0402                              | Murata Mfg. Co., Ltd.           | X7R                    |

| C3, C4, C6, C8, C9                                | 1000pF | 0402                              | Murata Mfg. Co., Ltd.           | C0G ceramic capacitors |

| C10, C11                                          | 150pF  | 0402                              | Murata Mfg. Co., Ltd.           | C0G ceramic capacitors |

| L1                                                | 470nH  | 1008                              | Coilcraft, Inc.                 | 1008CS-471XJLC         |

| R1                                                | 24Ω    | 0402                              | Vishay                          | 1%                     |

| R1A                                               | 10nF   | 0402                              | Murata Mfg. Co., Ltd.           | X7R                    |

| R2 (+3.3V applications only)                      | 1kΩ    | 0402                              | Panasonic Corp.                 | 1%                     |

| R3 (+3.3V applications only)                      | 2kΩ    | 0402                              | Panasonic Corp.                 | 1%                     |

| R4 (+5V applications and using internal DAC only) | 47kΩ   | 0402                              | Panasonic Corp.                 | 1%                     |

| U1                                                | _      | 40-pin thin QFN-EP<br>(6mm x 6mm) | Maxim Integrated Products, Inc. | MAX2067ETL+            |

### **Typical Application Circuit**

### Pin Configuration/Functional Block Diagram

#### **Chip Information**

### Package Information

PROCESS: SiGe BiCMOS

For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.

| PACKAGE TYPE   | PACKAGE CODE | DOCUMENT NO.   |

|----------------|--------------|----------------|

| 40 Thin QFN-EP | T4066-3      | <u>21-0141</u> |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

MAX2067ETL+ MAX2067ETL+T